# (19) 대한민국특허청(KR)(12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

**H01L 27/15** (2006.01) **H01L 33/00** (2010.01) **H01L 33/36** (2010.01) **H01L 33/50** (2010.01)

(52) CPC특허분류

*H01L 27/156* (2013.01) *H01L 33/005* (2013.01)

(21) 출원번호

10-2019-0087673

(22) 출원일자

2019년07월19일

심사청구일자 **없음**

(43) 공개일자

(71) 출원인

(11) 공개번호

엘지전자 주식회사

서울특별시 영등포구 여의대로 128 (여의도동)

10-2019-0092331

2019년08월07일

(72) 발명자

최환준

서울특별시 서초구 양재대로11길 19 LG전자 특허 센터

위경태

서울특별시 서초구 양재대로11길 19 LG전자 특허 센터

(74) 대리인

김용인, 방해철

전체 청구항 수 : 총 17 항

(54) 발명의 명칭 **마이크로 LED를 이용한 디스플레이 장치 및 이의 제조 방법**

#### (57) 요 약

본 명세서에서는 반도체 발광 소자의 도전형 전극부 및 그 주변부에만 이방 전도성 접착 페이스트층을 미리 형성하고, 이후 배선 기판에 전사하여, 전사와 동시에 안정적인 배선 공정을 수행하는 마이크로 LED디스플레이 장치및 이의 제조 방법을 개시한다. 여기서 본 발명의 일 실시예에 따른 복수의 반도체 발광 소자들을 이용하는 디스

## 대 표 도 - 도11

(뒷면에 계속)

플레이 장치는, 기판; 상기 기판 위에 위치하는 불규칙적인 요철 구조를 가지는 유기물 패드; 상기 유기물 패드 상에 위치하는 배선 전극; 상기 배선 전극 상에 위치하는 도전성 입자를 포함하는 이방 전도성 접착 페이스트층; 상기 이방 전도성 접착 페이스트층 상에 위치하고, 상기 페이스트층의 상기 도전성 입자에 의해 상기 배선 전극과 전기적으로 연결되는 반도체 발광 소자; 및 상기 배선 전극과 연결되지 않는 상기 반도체 발광 소자의 상측면에 구비되는 보호층을 포함하고, 상기 유기물 패드는 복수의 나노 파티클들을 포함하고, 상기 복수의 나노 파티클들 중 적어도 하나 이상의 나노 파티클이 상기 유기물 패드의 표면에 노출되는 구조를 가지는 것을 특징으로한다.

## (52) CPC특허분류

H01L 33/36 (2013.01) H01L 33/50 (2013.01) H01L 2224/1144 (2013.01)

## 명세서

## 청구범위

#### 청구항 1

반도체 발광 소자를 이용한 디스플레이 장치의 제조 방법에 있어서,

성장 기판에서 반도체 발광 소자를 형성하는 단계;

상기 반도체 발광 소자를 제 1임시 기판으로 전사하는 단계;

상기 제 1임시 기판의 상기 반도체 발광 소자를 보호층을 포함하는 제 2임시 기판으로 전사하는 단계;

상기 제 2임시 기판에 전사된 상기 반도체 발광 소자의 상측면에 이방 전도성 접착 페이스트층을 형성하는 단계;

상기 제 2임시 기판에 위치한 상기 반도체 발광 소자를 배선 전극이 형성된 배선 기판으로 전사하는 단계를 포함하되.

상기 배선 기판으로 전사된 상기 반도체 발광 소자는, 상기 배선 전극과 접촉하는 일면에는 상기 이방 전도성 접착 페이스트층을 구비하고, 상기 배선 전극과 접촉하지 않는 상기 반도체 발광 소자의 반대면은 보호층을 구 비하며,

상기 배선 전극은 불규칙한 요철 구조를 포함하는 것을 특징으로 하는 디스플레이 장치의 제조 방법.

#### 청구항 2

제 1항에 있어서,

상기 반도체 발광 소자를 형성하는 단계는,

제 1도전형 반도체층, 활성층 및 제 2도전형 반도체층을 포함하는 적층구조; 상기 적층구조의 상기 제 1도전형 반도체층과 전기적으로 연결되는 제 1도전형 전극; 및 상기 적층구조의 상기 제 2도전형 반도체층과 전기적으로 연결되는 제 2도전형 전극을 형성하는 단계를 포함하고,

상기 제 1 임시 기판으로 전사하는 단계는,

상기 반도체 발광 소자의 상기 제 1도전형 전극 및 상기 제 2도전형 전극이 상기 제 1임시 기판과 접촉하는 단계를 포함하는 디스플레이 장치의 제조 방법.

#### 청구항 3

제 2항에 있어서,

상기 제 2임시 기판으로 전사하는 단계는,

상기 반도체 발광 소자의 상기 제 2도전형 반도체충이 상기 제 2임시 기판의 상기 보호층과 접촉하는 단계를 포함하는 디스플레이 장치의 제조 방법.

#### 청구항 4

제 3항에 있어서,

상기 제 2임시 기판은

상기 보호층;

상기 보호층의 하부에 위치하는 릴리즈층(Release layer); 및

상기 릴리즈층의 하부에 위치하고, 상기 제 2임시 기판의 제 1영역에 선택적으로 형성되는 릴리즈(Release) 레이저 반사층을 포함하는 것을 특징으로 하는 디스플레이 장치의 제조 방법.

#### 청구항 5

제 4항에 있어서,

상기 제 2임시 기판은,

상기 제 2임시 기판과 수평 방향을 기준으로, 상기 반도체 발광 소자가 전사되지 않는 상기 제 1영역 및 상기 반도체 발광 소자가 전사되어, 위치하는 제 2영역을 포함하는 것을 특징으로 하는 디스플레이 장치의 제조 방법.

#### 청구항 6

제 5항에 있어서.

상기 배선 기판으로 전사하는 단계는,

상기 제 2임시 기판의 상기 보호층과 상기 제 2임시 기판의 상기 릴리즈층의 사이가 분리되는 단계; 및,

상기 반도체 발광 소자 및 상기 반도체 발광 소자와 접촉하는 상기 보호층이 상기 제 2임시 기판에서 분리되어, 상기 배선 기판으로 전사되는 단계를 포함하는 디스플레이 장치의 제조 방법.

## 청구항 7

제 6항에 있어서,

상기 보호층과 상기 릴리즈층의 사이가 분리되는 단계는,

상기 반도체 발광 소자가 전사되는 면이 아닌 상기 제 2임시 기판의 후면부로 UV(Ultra Violet) 또는 가시광 영역대의 레이저를 조사하는 단계; 및,

상기 릴리즈 레이저 반사층이 구비되지 않은 상기 제 2임시 기판의 상기 제 2영역에서, 상기 릴리즈층이 상기 조사된 레이저에 의해 계면 형상이 변형되는 단계; 를 포함하는 디스플레이 장치의 제조 방법.

#### 청구항 8

제 1항에 있어서,

상기 배선 전극은, 불규칙한 요철 구조를 포함하는 유기물 패드의 상부에 형성되고,

상기 유기물 패드는, 복수의 나노 파티클들을 포함하고, 상기 복수의 나노 파티클들 중 적어도 하나 이상의 나노 파티클이 상기 유기물 패드의 표면에 노출되는 구조를 가지는 것을 특징으로 하는 디스플레이 장치의 제조 방법.

#### 청구항 9

제 1항에 있어서,

상기 제 1 임시 기판은 돌기부를 포함하고,

상기 반도체 발광 소자를 상기 제 1 임시 기판으로 전사하는 단계는.

상기 반도체 발광 소자와 상기 돌기부가 오버랩되도록, 상기 성장 기판과 상기 제 1임시 기판을 얼라인(Align) 시키는 단계를 포함하는 디스플레이 장치의 제조 방법.

## 청구항 10

기판;

상기 기판 위에 위치하는 불규칙적인 요철 구조를 가지는 유기물 패드;

상기 유기물 패드 상에 위치하는 배선 전극;

상기 배선 전극 상에 위치하는 도전성 입자를 포함하는 이방 전도성 접착 페이스트층;

상기 이방 전도성 접착 페이스트층 상에 위치하고, 상기 페이스트층의 상기 도전성 입자에 의해 상기 배선 전극

과 전기적으로 연결되는 반도체 발광 소자; 및

상기 배선 전극과 연결되지 않는 상기 반도체 발광 소자의 상측면에 구비되는 보호층을 포함하고,

상기 유기물 패드는 복수의 나노 파티클들을 포함하고, 상기 복수의 나노 파티클들 중 적어도 하나 이상의 나노 파티클이 상기 유기물 패드의 표면에 노출되는 구조를 가지는 것을 특징으로 하는 디스플레이 장치.

## 청구항 11

제 10항에 있어서,

상기 반도체 발광 소자는,

제 1도전형 반도체층, 활성층, 제 2도전형 반도체층, 상기 제 1도전형 반도체층 상에 위치하는 제 1도전형 전극; 및

상기 제 1도전형 반도체층 및 상기 활성층의 일부가 식각되어 상기 제 2도전형 반도체층이 노출된 영역에 위치하는 제 2도전형 전극; 을 포함하는 수평형 반도체 발광 구조인 것을 특징으로 하는 디스플레이 장치.

#### 청구항 12

제 11항에 있어서,

상기 반도체 발광 소자의 상기 제 2도전형 반도체층은 상기 보호층과 접촉하고,

상기 반도체 발광 소자의 상기 제 1도전형 전극 및 상기 제 2도전형 전극은 상기 이방 전도성 접착 페이스트층 과 접촉하는 것을 특징으로 하는 디스플레이 장치.

#### 청구항 13

제 12항에 있어서,

상기 보호층은,

상기 제 2도전형 반도체층의 적어도 일 측면보다 돌출되어 형성되는 것을 특징으로 하는 디스플레이 장치.

## 청구항 14

제 10항에 있어서.

상기 보호층은 UV(Ultra Violet) 레진 또는 열경화성 레진인 것을 특징으로 하는 디스플레이 장치.

## 청구항 15

제 10항에 있어서.

상기 보호층의 제 1굴절율은 상기 반도체 발광 소자의 제 2굴절률보다 작은 것을 특징으로 하는 디스플레이 장치.

## 청구항 16

제 15항에 있어서,

상기 제 1굴절율은 1.5 내지 2.3 사이의 굴절율을 가지는 것을 특징으로 하는 디스플레이 장치.

## 청구항 17

제 1항에 있어서,

상기 반도체 발광 소자는 마이크로미터 단위의 크기를 가진 LED(Micro-LED)인 것을 특징으로 하는 디스플레이장치.

### 발명의 설명

## 기술분야

[0001] 본 발명은 디스플레이 장치 관련 기술 분야에 적용 가능하며, 예를 들어 마이크로 LED(Light Emitting Diode)를 이용한 디스플레이 장치 및 이의 제조 방법에 관한 것이다.

#### 배경기술

- [0002] 최근에는 디스플레이 기술 분야에서 박형, 플렉서블 등의 우수한 특성을 가지는 디스플레이 장치가 개발되고 있다. 이에 반해, 현재 상용화된 주요 디스플레이는 LCD(Liquid Crystal Display)와 OLED(Organic Light Emitting Diodes)로 대표되고 있다.

- [0003] 그러나, LCD의 경우에 빠르지 않은 반응 시간과, 플렉서블의 구현이 어렵다는 문제점이 있고, OLED의 경우에 수명이 짧고, 양산 수율이 좋지 않다는 문제점이 있다.

- [0004] 한편, 발광 다이오드(Light Emitting Diode: LED)는 전류를 빛으로 변환시키는 것으로 잘 알려진 반도체 발광소자로서, 1962년 GaAsP 화합물 반도체를 이용한 적색 LED가 상품화된 것을 시작으로 GaP:N 계열의 녹색 LED와함께 정보 통신기기를 비롯한 전자장치의 표시 화상용 광원으로 이용되어 왔다. 따라서, 상기 반도체 발광소자를 이용하여 디스플레이를 구현하여, 전술한 문제점을 해결하는 방안이 제시될 수 있다. 상기 반도체 발광소자는 필라멘트 기반의 발광소자에 비해 긴 수명, 낮은 전력소모, 우수한초기구동특성, 및높은 진동저항등의 다양한 장점을 갖는다.

- [0005] 하지만 반도체 발광 소자를 이용하여 대면적 고화소 디스플레이 장치를 구현하기 위해서는 매우 많은 수의 반도 체 발광 소자들이 상기 디스플레이 장치의 배선 기판에 안정적으로 조립 또는 전사되어야 한다.

- [0006] 또한 상기 조립 또는 전사 이후, 상기 배선 기판과 상기 반도체 발광 소자를 전기적으로 연결하는 배선 공정에 서 발생하게 되는 불량 이슈를 최소화 시켜야 한다.

- [0007] 이에, 본 발명에서는 반도체 발광 소자가 안정적으로 배선 기판에 전사되고, 이와 동시에 배선 공정이 수행되는 새로운 형태의 디스플레이 장치 및 그 제조 방법을 제시한다.

## 발명의 내용

#### 해결하려는 과제

- [0008] 본 발명의 일 실시예의 목적은, 반도체 발광 소자를 이용한 디스플레이 장치 및 제조 방법을 제공하는 것이다.

- [0009] 본 발명의 일 실시예의 다른 목적은, 반도체 발광 소자를 디스플레이 기판에 전사함과 동시에 안정적으로 배선 공정이 수행되는 디스플레이 장치 및 이의 제조 방법을 제공하는 것이다.

- [0010] 나아가, 본 발명의 일 실시예의 또 다른 목적은, 여기에서 언급하지 않은 다양한 문제점들도 해결하고자 한다. 당업자는 명세서 및 도면의 전 취지를 통해 이해할 수 있다.

## 과제의 해결 수단

- [0011] 상기 목적을 달성하기 위한 반도체 발광 소자를 이용한 디스플레이 장치의 제조 방법은, 성장 기판에서 반도체 발광 소자를 형성하는 단계; 상기 반도체 발광 소자를 제 1 임시 기판으로 전사하는 단계; 상기 제 1임시 기판의 상기 반도체 발광 소자를 보호층을 포함하는 제 2임시 기판으로 전사하는 단계; 상기 제 2임시 기판에 전사된 상기 반도체 발광 소자의 상측면에 이방 전도성 접착 페이스트층을 형성하는 단계; 상기 제 2임시 기판에 위치한 상기 반도체 발광 소자를 배선 전극이 형성된 배선 기판으로 전사하는 단계를 포함하되, 상기 배선 기판으로 전사된 상기 반도체 발광 소자를 배선 전극이 형성된 배선 기판으로 전사하는 단계를 포함하되, 상기 배선 기판으로 전사된 상기 반도체 발광 소자는, 상기 배선 전극과 접촉하는 일면에는 상기 이방 전도성 접착 페이스트층을 구비하고, 상기 배선 전극과 접촉하지 않는 상기 반도체 발광 소자의 반대면은 보호층을 구비하며, 상기 배선 전극은 불규칙한 요철 구조를 포함하는 것을 특징으로 한다.

- [0012] 실시예로서, 상기 반도체 발광 소자를 형성하는 단계는, 제 1도전형 반도체충, 활성충 및 제 2도전형 반도체충을 포함하는 적충구조; 상기 적충구조의 상기 제 1도전형 반도체충과 전기적으로 연결되는 제 1도전형 전극; 및 상기 적충구조의 상기 제 2도전형 반도체충과 전기적으로 연결되는 제 2도전형 전극을 형성하는 단계를 포함하고, 상기 제 1 임시 기판으로 전사하는 단계는, 상기 반도체 발광 소자의 상기 제 1도전형 전극 및 상기 제 2도 전형 전극이 상기 제 1임시 기판과 접촉하는 단계를 포함한다.

- [0013] 실시예로서, 상기 제 2임시 기판으로 전사하는 단계는, 상기 반도체 발광 소자의 상기 제 2도전형 반도체층이

상기 제 2임시 기판의 상기 보호층과 접촉하는 단계를 포함한다.

- [0014] 실시예로서, 상기 제 2임시 기판은 상기 보호층; 상기 보호층의 하부에 위치하는 릴리즈층(Release layer); 및 상기 릴리즈층의 하부에 위치하고, 상기 제 2임시 기판의 제 1영역에 선택적으로 형성되는 릴리즈(Release) 레이저 반사층을 포함하는 것을 특징으로 한다.

- [0015] 실시예로서, 상기 제 2임시 기판은, 상기 제 2임시 기판과 수평 방향을 기준으로, 상기 반도체 발광 소자가 전 사되지 않는 상기 제 1영역 및 상기 반도체 발광 소자가 전사되어, 위치하는 제 2영역을 포함하는 것을 특징으로 한다.

- [0016] 실시예로서, 상기 배선 기판으로 전사하는 단계는, 상기 제 2임시 기판의 상기 보호층과 상기 제 2임시 기판의 상기 릴리즈층의 사이가 분리되는 단계; 및, 상기 반도체 발광 소자 및 상기 반도체 발광 소자와 접촉하는 상기 보호층이 상기 제 2임시 기판에서 분리되어, 상기 배선 기판으로 전사되는 단계를 포함한다.

- [0017] 실시예로서, 상기 보호층과 상기 릴리즈층의 사이가 분리되는 단계는, 상기 반도체 발광 소자가 전사되는 면이 아닌 상기 제 2임시 기판의 후면부로 UV(Ultra Violet) 또는 가시광 영역대의 레이저를 조사하는 단계; 및, 상기 릴리즈 레이저 반사층이 구비되지 않은 상기 제 2임시 기판의 상기 제 2영역에서, 상기 릴리즈층이 상기 조사된 레이저에 의해 계면 형상이 변형되는 단계를 포함한다.

- [0018] 실시예로서, 상기 배선 전극은, 불규칙한 요철 구조를 포함하는 유기물 패드의 상부에 형성되고, 상기 유기물 패드는, 복수의 나노 파티클들을 포함하고, 상기 복수의 나노 파티클들 중 적어도 하나 이상의 나노 파티클이 상기 유기물 패드의 표면에 노출되는 구조를 가지는 것을 특징으로 한다.

- [0019] 실시예로서, 상기 제 1 임시 기판은 돌기부를 포함하고, 상기 반도체 발광 소자를 상기 제 1 임시 기판으로 전 사하는 단계는, 상기 반도체 발광 소자와 상기 돌기부가 오버랩되도록, 상기 성장 기판과 상기 제 1임시 기판을 얼라인(Align) 시키는 단계를 포함한다.

- [0020] 본 발명의 다른 실시예에 따른 복수의 반도체 발광 소자들을 이용한 디스플레이 장치는, 기판; 상기 기판 위에 위치하는 불규칙적인 요철 구조를 가지는 유기물 패드; 상기 유기물 패드 상에 위치하는 배선 전극; 상기 배선 전극 상에 위치하는 도전성 입자를 포함하는 이방 전도성 접착 페이스트층; 상기 이방 전도성 접착 페이스트층 상에 위치하고, 상기 페이스트층의 상기 도전성 입자에 의해 상기 배선 전극과 전기적으로 연결되는 반도체 발광 소자; 및 상기 배선 전극과 연결되지 않는 상기 반도체 발광 소자의 상측면에 구비되는 보호층을 포함하고, 상기 유기물 패드는 복수의 나노 파티클들을 포함하고, 상기 복수의 나노 파티클들 중 적어도 하나 이상의 나노 파티클이 상기 유기물 패드의 표면에 노출되는 구조를 가지는 것을 특징으로 한다.

- [0021] 실시예로서, 상기 반도체 발광 소자는, 제 1도전형 반도체층, 활성층, 제 2도전형 반도체층, 상기 제 1도전형 반도체층 상에 위치하는 제 1도전형 전극; 및 상기 제 1도전형 반도체층 및 상기 활성층의 일부가 식각되어 상기 제 2도전형 반도체층이 노출된 영역에 위치하는 제 2도전형 전극; 을 포함하는 수평형 반도체 발광 구조인 것을 특징으로 한다.

- [0022] 실시예로서, 상기 반도체 발광 소자의 상기 제 2도전형 반도체층은 상기 보호층과 접촉하고, 상기 반도체 발광 소자의 상기 제 1도전형 전극 및 상기 제 2도전형 전극은 상기 이방 전도성 접착 페이스트층과 접촉하는 것을 특징으로 한다.

- [0023] 실시예로서, 상기 보호층은 상기 제 2도전형 반도체층의 적어도 일 측면보다 돌출되어 형성되는 것을 특징으로 한다.

- [0024] 실시예로서, 상기 보호층은 UV(Ultra Violet) 레진 또는 열경화성 레진인 것을 특징으로 한다.

- [0025] 실시예로서, 상기 보호층의 제 1굴절율은 상기 반도체 발광 소자의 제 2굴절률보다 작은 것을 특징으로 한다.

- [0026] 실시예로서, 상기 제 1굴절율은 1.5 내지 2.3 사이의 굴절율을 가지는 것을 특징으로 한다.

- [0027] 실시예로서, 상기 반도체 발광 소자는 마이크로미터 단위의 크기를 가진 LED(Micro-LED)인 것을 특징으로 한다.

# 발명의 효과

- [0028] 본 발명의 일 실시예에 따르면, 반도체 발광 소자를 이용한 디스플레이 장치 및 제조 방법을 제공할 수 있다.

- [0029] 구체적으로, 배선 기판으로 전사되는 반도체 발광 소자는 상기 반도체 발광 소자의 도전형 전극 및 그 주변부에

만 이방 전도성 접착 페이스트층이 기 형성된다. 따라서 상기 배선 기판 내 배선 전극의 위치에 상기 반도체 발 광 소자가 전사되는 되는 경우, 소자 간 쇼트 불량 위험 없이 배선 공정이 수행되는 효과가 있다.

- [0030] 또한, 상기 배선 전극은 불규칙한 요철 구조 및 하부에 유기물 패드를 구비하여, 상기 이방 전도성 접착 페이스 트층과 압착 시, 상기 페이스트층 내 도전성 입자와 접촉 면적을 증가시키고, 압착에 의한 충격을 완화시킨다. 따라서 상기 반도체 발광 소자가 상기 배선 전극에 안정적으로 전사되는 효과가 있다.

- [0031] 나아가, 본 발명의 또 다른 실시예에 따르면, 여기에서 언급하지 않은 추가적인 기술적 효과들도 있다. 당업자 는 명세서 및 도면의 전 취지를 통해 이해할 수 있다.

## 도면의 간단한 설명

- [0032] 도 1은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 일 실시예를 나타내는 개념도이다.

- 도 2는 도 1의 A부분의 부분 확대도 이다.

- 도 3a 및 도 3b는 도 2의 라인 B-B 및 C-C를 따라 절단된 단면도들이다.

- 도 4는 도 3의 플립 칩 타입 반도체 발광 소자를 나타내는 개념도이다.

- 도 5a 내지 도 5c는 플립 칩 타입 반도체 발광 소자와 관련하여 컬러를 구현하는 여러 가지 형태를 나타내는 개념도들이다.

- 도 6은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 제조방법을 나타낸 단면도들이다.

- 도 7은 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 다른 일 실시예를 나타내는 사시도이다.

- 도 8은 도 7의 라인 D-D를 따라 절단된 단면도이다.

- 도 9는 도 8의 수직형 반도체 발광 소자를 나타내는 개념도이다.

- 도 10은 본 발명의 다른 실시예에 따른 반도체 발광 소자를 이용한 디스플레이 장치를 설명하기 위한, 도 1의 A 부분의 확대도이다.

- 도 12는 도 11의 E부분을 확대한 도면이다.

- 도 13은 도10의 디스플레이 장치를 제작하는 과정을 나타내는 순서도이다.

- 도 14는 도 10의 반도체 발광 소자를 성장 기판에서 형성하는 과정을 나타내는 단면도들이다.

- 도 15는 도14의 반도체 발광 소자를 제 1임시 기판으로 전사하는 과정을 나타내는 도면들이다.

- 도 16은 도15의 반도체 발광 소자를 제 2임시 기판으로 전사하는 과정을 나타내는 도면들이다.

- 도 17은 도16의 제 2임시 기판 상의 반도체 발광 소자에 이방 전도성 접착 페이스트층을 형성한 이후의 단면도 이다.

- 도 18은 도17의 반도체 발광 소자를 배선 기판으로 전사하는 과정을 나타내는 도면들이다.

- 도 19은 도18의 반도체 발광 소자가 배선 기판으로 전사되는 과정을 구체적으로 나타내는 순서도이다.

- 도 20은 반도체 발광 소자 및 이방 전도성 접착 페이스트층의 선택적 전사를 위해 제 2임시 기판에 다중 레이어 구조를 형성하는 과정을 나타내는 순서도이다.

- 도 21은 도 20의 방법에 의해 형성된 제 2임시 기판의 다중 레이어 구조를 나타내는 단면도이다.

- 도 22는 불규칙한 요철 구조를 구비한 배선 전극을 제작하는 과정을 나타내는 순서도이다.

- 도 23은 불규칙한 요철 구조를 구비한 배선 전극을 제작하는 과정을 나타내는 단면도들이다.

#### 발명을 실시하기 위한 구체적인 내용

[0033] 이하, 첨부된 도면을 참조하여 본 명세서에 개시된 실시 예를 상세히 설명하되, 도면 부호에 관계없이 동일하거나 유사한 구성요소는 동일한 참조 번호를 부여하고 이에 대한 중복되는 설명은 생략하기로 한다. 이하의 설명에서 사용되는 구성요소에 대한 접미사 "모듈" 및 "부"는 명세서 작성의 용이함만이 고려되어 부여되거나 혼용되는 것으로서, 그 자체로 서로 구별되는 의미 또는 역할을 갖는 것은 아니다. 또한, 본 명세서에 개시된 실시

예를 설명함에 있어서 관련된 공지기술에 대한 구체적인 설명이 본 명세서에 개시된 실시 예의 요지를 흐릴 수 있다고 판단되는 경우 그 상세한 설명을 생략한다. 또한, 첨부된 도면은 본 명세서에 개시된 실시 예를 쉽게 이해할 수 있도록 하기 위한 것일 뿐, 첨부된 도면에 의해 본 명세서에 개시된 기술적 사상이 제한되는 것으로 해석되어서는 아니 됨을 유의해야 한다.

- [0034] 나아가, 설명의 편의를 위해 각각의 도면에 대해 설명하고 있으나, 당업자가 적어도 2개 이상의 도면을 결합하여 다른 실시예를 구현하는 것도 본 발명의 권리범위에 속한다.

- [0035] 또한, 층, 영역 또는 기판과 같은 요소가 다른 구성요소 "상(on)"에 존재하는 것으로 언급될 때, 이것은 직접적으로 다른 요소 상에 존재하거나 또는 그 사이에 중간 요소가 존재할 수도 있다는 것을 이해할 수 있을 것이다.

- [0036] 본 명세서에서 설명되는 디스플레이 장치는 단위 화소 또는 단위 화소의 집합으로 정보를 표시하는 모든 디스플레이 장치를 포함하는 개념이다. 따라서 완성품에 한정하지 않고 부품에도 적용될 수 있다. 예를 들어 디지털 TV의 일 부품에 해당하는 패널도 독자적으로 본 명세서 상의 디스플레이 장치에 해당한다. 완성품으로는 휴대폰, 스마트 폰(smart phone), 노트북 컴퓨터(laptop computer), 디지털방송용 단말기, PDA(personal digital assistants), PMP(portable multimedia player), 네비케이션, 슬레이트 피씨(Slate PC), Tablet PC, Ultra Book, 디지털 TV, 데스크 탑 컴퓨터 등이 포함될 수 있다.

- [0037] 그러나, 본 명세서에 기재된 실시예에 따른 구성은 추후 개발되는 새로운 제품 형태라도, 디스플레이가 가능한 장치에는 적용될 수도 있음을 본 기술 분야의 당업자라면 쉽게 알 수 있을 것이다.

- [0038] 또한, 당해 명세서에서 언급된 반도체 발광 소자는 LED, 마이크로 LED 등을 포함하는 개념이며, 혼용되어 사용될 수 있다.

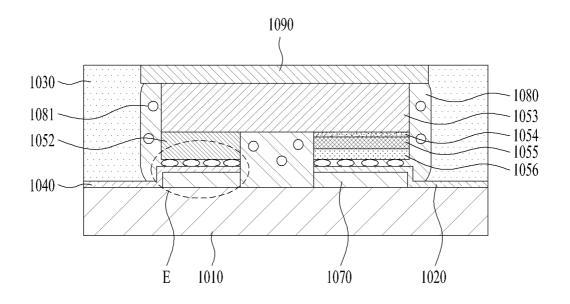

- [0039] 도 1은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 일실시예를 나타내는 개념도이다.

- [0040] 도 1에 도시된 바와 같이, 디스플레이 장치(100)의 제어부(미도시)에서 처리되는 정보는 플렉서블 디스플레이 (flexible display)를 이용하여 표시될 수 있다.

- [0041] 플렉서블 디스플레이는, 예를 들어 외력에 의하여 휘어질 수 있는, 또는 구부러질 수 있는, 또는 비틀어질 수 있는, 또는 접힐 수 있는, 또는 말려질 수 있는 디스플레이를 포함한다.

- [0042] 나아가, 플렉서블 디스플레이는, 예를 들어 기존의 평판 디스플레이의 디스플레이 특성을 유지하면서, 종이와 같이 휘어지거나, 또는 구부리거나, 또는 접을 수 있거나 또는 말 수 있는 얇고 유연한 기판 위에 제작되는 디스플레이가 될 수 있다.

- [0043] 상기 플렉서블 디스플레이가 휘어지지 않는 상태(예를 들어, 무한대의 곡률반경을 가지는 상태, 이하 제1상태라한다)에서는 상기 플렉서블 디스플레이의 디스플레이 영역이 평면이 된다. 상기 제1상태에서 외력에 의하여 휘어진 상태(예를 들어, 유한의 곡률 반경을 가지는 상태, 이하, 제2상태라 한다)에서는 상기 디스플레이 영역이 곡면이 될 수 있다. 도 1에 도시된 바와 같이, 상기 제2상태에서 표시되는 정보는 곡면상에 출력되는 시각 정보가 될 수 있다. 이러한 시각 정보는 매트릭스 형태로 배치되는 단위 화소(sub-pixel)의 발광이 독자적으로 제어됨에 의하여 구현된다. 상기 단위 화소는, 예를 들어 하나의 색을 구현하기 위한 최소 단위를 의미한다.

- [0044] 상기 플렉서블 디스플레이의 단위 화소는 반도체 발광 소자에 의하여 구현될 수 있다. 본 발명에서는 전류를 빛으로 변환시키는 반도체 발광 소자의 일 종류로서 발광 다이오드(Light Emitting Diode: LED)를 예시한다. 상기 발광 다이오드는 작은 크기로 형성되며, 이를 통하여 상기 제2상태에서도 단위 화소의 역할을 할 수 있게 된다.

- [0045] 상기 발광 다이오드를 이용하여 구현된 플렉서블 디스플레이에 대하여, 이하 도면들을 참조하여 보다 상세히 설명한다.

- [0046] 도 2는 도 1의 A부분의 부분 확대도 이다.

- [0047] 도 3a 및 도 3b는 도 2의 라인 B-B 및 C-C를 따라 절단된 단면도들이다.

- [0048] 도 4는 도 3의 플립 칩 타입 반도체 발광 소자를 나타내는 개념도이다.

- [0049] 도 5a 내지 도 5c는 플립 칩 타입 반도체 발광 소자와 관련하여 컬러를 구현하는 여러 가지 형태를 나타내는 개 념도들이다.

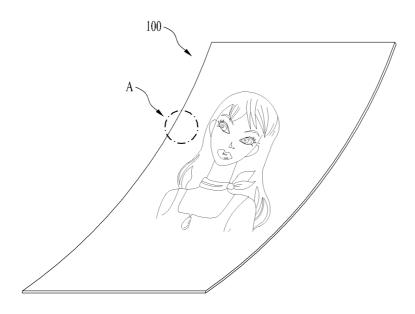

- [0050] 도 2, 도 3a 및 도 3b에 도시된 바와 같이, 반도체 발광 소자를 이용한 디스플레이 장치(100)로서 패시브 매트릭스(Passive Matrix, PM) 방식의 반도체 발광 소자를 이용한 디스플레이 장치(100)를 예시한다. 다만, 이하 설

명되는 예시는 액티브 매트릭스(Active Matrix, AM) 방식의 반도체 발광 소자에도 적용 가능하다.

- [0051] 도 1에 도시된 디스플레이 장치(100)는, 도 2에 도시된 바와 같이 기판(110), 제1전극(120), 전도성 접착층 (130), 제2전극(140) 및 적어도 하나의 반도체 발광 소자(150)를 포함한다.

- [0052] 기판(110)은 플렉서블 기판일 수 있다. 예를 들어, 플렉서블(flexible) 디스플레이 장치를 구현하기 위하여 기판(110)은 유리나 폴리이미드(PI, Polyimide)를 포함할 수 있다. 이외에도 절연성이 있고, 유연성 있는 재질이면, 예를 들어 PEN(Polyethylene Naphthalate), PET(Polyethylene Terephthalate) 등 어느 것이라도 사용될 수있다. 또한, 상기 기판(110)은 투명한 재질 또는 불투명한 재질 어느 것이나 될 수 있다.

- [0053] 상기 기판(110)은 제1전극(120)이 배치되는 배선기판이 될 수 있으며, 따라서 상기 제1전극(120)은 기판(110) 상에 위치할 수 있다.

- [0054] 도 3a에 도시된 바와 같이 절연층(160)은 제1전극(120)이 위치한 기판(110) 상에 배치될 수 있으며, 상기 절연 층(160)에는 보조전극(170)이 위치할 수 있다. 이 경우에, 상기 기판(110)에 절연층(160)이 적충된 상태가 하나의 배선기판이 될 수 있다. 보다 구체적으로, 절연층(160)은 폴리이미드(PI, Polyimide), PET, PEN 등과 같이 절연성이 있고, 유연성 있는 재질로, 상기 기판(110)과 일체로 이루어져 하나의 기판을 형성할 수 있다.

- [0055] 보조전극(170)은 제1전극(120)과 반도체 발광 소자(150)를 전기적으로 연결하는 전극으로서, 절연층(160) 상에 위치하고, 제1전극(120)의 위치에 대응하여 배치된다. 예를 들어, 보조전극(170)은 닷(dot) 형태이며, 절연층 (160)을 관통하는 전극홀(171)에 의하여 제1전극(120)과 전기적으로 연결될 수 있다. 상기 전극홀(171)은 비아홀에 도전물질이 채워짐에 의하여 형성될 수 있다.

- [0056] 도 2 또는 도 3a에 도시된 바와 같이, 절연층(160)의 일면에는 전도성 접착층(130)이 형성되나, 본 발명은 반드시 이에 한정되는 것은 아니다. 예를 들어, 절연층(160)과 전도성 접착층(130)의 사이에 특정 기능을 수행하는 레이어가 형성되거나, 절연층(160)이 없이 전도성 접착층(130)이 기판(110)상에 배치되는 구조도 가능하다. 전도성 접착층(130)이 기판(110)상에 배치되는 구조에서는 전도성 접착층(130)이 절연층의 역할을 할 수 있다.

- [0057] 상기 전도성 접착충(130)은 접착성과 전도성을 가지는 충이 될 수 있으며, 이를 위하여 상기 전도성 접착충 (130)에서는 전도성을 가지는 물질과 접착성을 가지는 물질이 혼합될 수 있다. 또한 전도성 접착충(130)은 연성을 가지며, 이를 통하여 디스플레이 장치에서 플렉서블 기능을 가능하게 한다.

- [0058] 이러한 예로서, 전도성 접착층(130)은 이방성 전도성 필름(anistropy conductive film, ACF), 이방성 전도 페이스트(paste), 전도성 입자를 함유한 솔루션(solution) 등이 될 수 있다. 상기 전도성 접착층(130)은 두께를 관통하는 Z 방향으로는 전기적 상호 연결을 허용하나, 수평적인 X-Y 방향으로는 전기 절연성을 가지는 레이어로서 구성될 수 있다. 따라서 상기 전도성 접착층(130)은 Z축 전도층으로 명명될 수 있다(다만, 이하 '전도성 접착층'이라 한다).

- [0059] 상기 이방성 전도성 필름은 이방성 전도매질(anisotropic conductive medium)이 절연성 베이스부재에 혼합된 형태의 필름으로서, 열 및 압력이 가해지면 특정 부분만 이방성 전도매질에 의하여 전도성을 가지게 된다. 이하, 상기 이방성 전도성 필름에는 열 및 압력이 가해지는 것으로 설명하나, 상기 이방성 전도성 필름이 부분적으로 전도성을 가지기 위하여 다른 방법이 적용될 수도 있다. 전술한 다른 방법은, 예를 들어 상기 열 및 압력 중 어느 하나만이 가해지거나 UV 경화 등이 될 수 있다.

- [0060] 또한, 상기 이방성 전도매질은 예를 들어, 도전볼이나 전도성 입자가 될 수 있다. 예를 들어, 상기 이방성 전도 성 필름은 도전볼이 절연성 베이스 부재에 혼합된 형태의 필름으로서, 열 및 압력이 가해지면 특정 부분만 도전 볼에 의하여 전도성을 가지게 된다. 이방성 전도성 필름은 전도성 물질의 코어가 폴리머 재질의 절연막에 의하여 피복된 복수의 입자가 함유된 상태가 될 수 있으며, 이 경우에 열 및 압력이 가해진 부분이 절연막이 파괴되면서 코어에 의하여 도전성을 가지게 된다. 이때, 코어의 형태는 변형되어 필름의 두께방향으로 서로 접촉하는 층을 이룰 수 있다. 보다 구체적인 예로서, 열 및 압력은 이방성 전도성 필름에 전체적으로 가해지며, 이방성 전도성 필름에 의하여 접착되는 상대물의 높이 차에 의하여 Z축 방향의 전기적 연결이 부분적으로 형성된다.

- [0061] 다른 예로서, 이방성 전도성 필름은 절연 코어에 전도성 물질이 피복된 복수의 입자가 함유된 상태가 될 수 있다. 이 경우에는 열 및 압력이 가해진 부분이 전도성 물질이 변형되어(눌러 붙어서) 필름의 두께방향으로 전도성을 가지게 된다. 또 다른 예로서, 전도성 물질이 Z축 방향으로 절연성 베이스 부재를 관통하여 필름의 두께방향으로 전도성을 가지는 형태도 가능하다. 이 경우에, 전도성 물질은 뽀족한 단부를 가질 수 있다.

- [0062] 상기 이방성 전도성 필름은 도전볼이 절연성 베이스 부재의 일면에 삽입된 형태로 구성되는 고정배열 이방성 전

도성 필름(fixed array ACF)이 될 수 있다. 보다 구체적으로, 절연성 베이스 부재는 접착성을 가지는 물질로 형성되며, 도전볼은 상기 절연성 베이스 부재의 바닥 부분에 집중적으로 배치되며, 상기 베이스 부재에서 열 및 압력이 가해지면 상기 도전볼과 함께 변형됨에 따라 수직 방향으로 전도성을 가지게 된다.

- [0063] 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 상기 이방성 전도성 필름은 절연성 베이스 부재에 도전볼 이 랜덤하게 혼입된 형태나, 복수의 층으로 구성되며 어느 한 층에 도전볼이 배치되는 형태(double-ACF) 등이 모두 가능하다.

- [0064] 이방성 전도 페이스트는 페이스트와 도전볼의 결합 형태로서, 절연성 및 접착성의 베이스 물질에 도전볼이 혼합된 페이스트가 될 수 있다. 또한, 전도성 입자를 함유한 솔루션은 전도성 파티클 혹은 나노 입자를 함유한 형태의 솔루션이 될 수 있다.

- [0065] 다시 도3a를 참조하면, 제2전극(140)은 보조전극(170)과 이격하여 절연층(160)에 위치한다. 즉, 상기 전도성 접착층(130)은 보조전극(170) 및 제2전극(140)이 위치하는 절연층(160) 상에 배치된다.

- [0066] 절연층(160)에 보조전극(170)과 제2전극(140)이 위치된 상태에서 전도성 접착층(130)을 형성한 후에, 반도체 발광 소자(150)를 열 및 압력을 가하여 플립 칩 형태로 접속시키면, 상기 반도체 발광 소자(150)는 제1전극(120) 및 제2전극(140)과 전기적으로 연결된다.

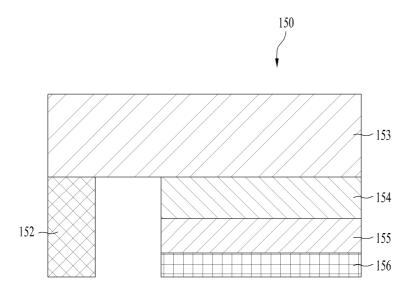

- [0067] 도 4를 참조하면, 상기 반도체 발광 소자는 플립 칩 타입(flip chiptype)의 발광 소자가 될 수 있다.

- [0068] 예를 들어, 상기 반도체 발광 소자는 p형 전극(156), p형 전극(156)이 형성되는 p형 반도체층(155), p형 반도체 층(155) 상에 형성된 활성층(154), 활성층(154) 상에 형성된 n형 반도체층(153) 및 n형 반도체층(153) 상에서 p 형 전극(156)과 수평방향으로 이격 배치되는 n형 전극(152)을 포함한다. 이 경우, p형 전극(156)은 도3에 도시된, 보조전극(170)과 전도성 접착층(130)에 의하여 전기적으로 연결될 수 있고, n형 전극(152)은 제2전극(140)과 전기적으로 연결될 수 있다.

- [0069] 다시 도 2, 도 3a 및 도 3b를 참조하면, 보조전극(170)은 일방향으로 길게 형성되어, 하나의 보조전극이 복수의 반도체 발광 소자(150)에 전기적으로 연결될 수 있다. 예를 들어, 보조전극을 중심으로 좌우의 반도체 발광 소자들의 p 형 전극들이 하나의 보조전극에 전기적으로 연결될 수 있다.

- [0070] 보다 구체적으로, 열 및 압력에 의하여 전도성 접착층(130)의 내부로 반도체 발광 소자(150)가 압입되며 이를 통하여 반도체 발광 소자(150)의 p형 전극(156)과 보조전극(170) 사이의 부분과, 반도체 발광 소자(150)의 n형 전극(152)과 제2전극(140) 사이의 부분에서만 전도성을 가지게 되고, 나머지 부분에서는 반도체 발광 소자의 압입이 없어 전도성을 가지지 않게 된다. 이와 같이, 전도성 접착층(130)은 반도체 발광 소자(150)와 보조전극(170) 사이 및 반도체 발광 소자(150)와 제2전극(140) 사이를 상호 결합시켜줄 뿐만 아니라 전기적 연결까지 형성시킨다.

- [0071] 또한, 복수의 반도체 발광 소자(150)는 발광 소자 어레이(array)를 구성하며, 발광 소자 어레이에는 형광체층 (180)이 형성된다.

- [0072] 발광 소자 어레이는 자체 휘도 값이 상이한 복수의 반도체 발광 소자들을 포함할 수 있다. 각각의 반도체 발광 소자(150)는 단위 화소를 구성하며, 제1전극(120)에 전기적으로 연결된다. 예를 들어, 제1전극(120)은 복수 개일 수 있고, 반도체 발광 소자들은 예컨대 수 열로 배치되며, 각 열의 반도체 발광 소자들은 상기 복수 개의 제 1전극 중 어느 하나에 전기적으로 연결될 수 있다.

- [0073] 또한, 반도체 발광 소자들이 플립 칩 형태로 접속되므로, 투명 유전체 기판에 성장시킨 반도체 발광 소자들을 이용할 수 있다. 또한, 상기 반도체 발광 소자들은 예컨대 질화물 반도체 발광 소자일 수 있다. 반도체 발광 소자(150)는 휘도가 우수하므로, 작은 크기로도 개별 단위 화소를 구성할 수 있다.

- [0074] 도3에 도시된 바와 같이, 반도체 발광 소자(150)의 사이에 격벽(190)이 형성될 수 있다. 이 경우, 격벽(190)은 개별 단위 화소를 서로 분리하는 역할을 할 수 있으며, 전도성 접착층(130)과 일체로 형성될 수 있다. 예를 들어, 이방성 전도성 필름에 반도체 발광 소자(150)가 삽입됨에 의하여 이방성 전도성 필름의 베이스 부재가 상기 격벽을 형성할 수 있다.

- [0075] 또한, 상기 이방성 전도성 필름의 베이스 부재가 블랙이면, 별도의 블랙 절연체가 없어도 상기 격벽(190)이 반사 특성을 가지는 동시에 대비비(contrast)가 증가될 수 있다.

- [0076] 다른 예로서, 상기 격벽(190)으로 반사성 격벽이 별도로 구비될 수 있다. 이 경우에, 상기 격벽(190)은 디스플

레이 장치의 목적에 따라 블랙(Black) 또는 화이트(White) 절연체를 포함할 수 있다. 화이트 절연체의 격벽을 이용할 경우 반사성을 높이는 효과가 있을 수 있고, 블랙 절연체의 격벽을 이용할 경우, 반사 특성을 가지는 동시에 대비비(contrast)를 증가시킬 수 있다.

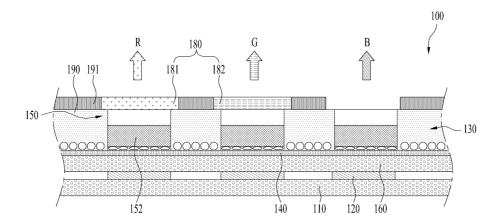

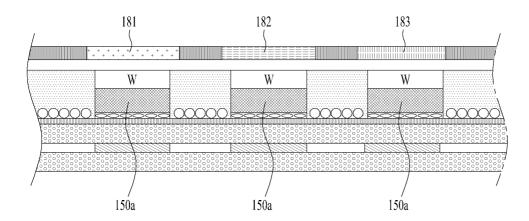

- [0077] 형광체층(180)은 반도체 발광 소자(150)의 외면에 위치할 수 있다. 예를 들어, 반도체 발광 소자(150)는 청색(B) 광을 발광하는 청색 반도체 발광 소자고, 형광체층(180)은 상기 청색(B) 광을 단위 화소의 색상으로 변환시키는 기능을 수행한다. 상기 형광체층(180)은 개별 화소를 구성하는 적색 형광체(181) 또는 녹색 형광체(182)가될 수 있다.

- [0078] 즉, 적색의 단위 화소를 이루는 위치에서, 청색 반도체 발광 소자 상에는 청색 광을 적색(R) 광으로 변환시킬 수 있는 적색 형광체(181)가 적충될 수 있고, 녹색의 단위 화소를 이루는 위치에서는, 청색 반도체 발광 소자 상에 청색광을 녹색(G) 광으로 변환시킬 수 있는 녹색 형광체(182)가 적충될 수 있다. 또한, 청색의 단위 화소를 이루는 부분에는 청색 반도체 발광 소자만 단독으로 이용될 수 있다. 이 경우, 적색(R), 녹색(G), 및 청색(B)의 단위 화소들이 하나의 화소를 이룰 수 있다. 보다 구체적으로, 제1전극(120)의 각 라인을 따라 하나의 색상의 형광체가 적충될 수 있다. 따라서, 제1전극(120)에서 하나의 라인은 하나의 색상을 제어하는 전극이 될 수 있다. 즉, 제2전극(140)을 따라서, 적색(R), 녹색(G) 및 청색(B)이 차례로 배치될 수 있으며, 이를 통하여 단위화소가 구현될 수 있다.

- [0079] 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 형광체 대신에 반도체 발광 소자(150)와 퀀텀닷(QD)이 조합되어 적색(R), 녹색(G) 및 청색(B)의 단위 화소들을 구현할 수 있다.

- [0080] 또한, 대비비(contrast) 향상을 위하여 각각의 형광체충들의 사이에는 블랙 매트릭스(191)가 배치될 수 있다. 즉, 이러한 블랙 매트릭스(191)는 명암의 대조를 향상시킬 수 있다.

- [0081] 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 청색, 적색, 녹색을 구현하기 위한 다른 구조가 적용될 수있다.

- [0082] 도 5a를 참조하면, 각각의 반도체 발광 소자(150)는 질화 갈륨(GaN)을 주재료로 하여, 인듐(In) 및/또는 알루미늄(Al)이 함께 첨가되어 청색을 비롯한 다양한 빛을 발광하는 고출력의 발광 소자로 구현될 수 있다.

- [0083] 이 경우, 반도체 발광 소자(150)는 각각 단위 화소(sub-pixel)를 이루기 위하여 적색, 녹색 및 청색 반도체 발광 소자일 수 있다. 예컨대, 적색, 녹색 및 청색 반도체 발광 소자(R, G, B)가 교대로 배치되고, 적색, 녹색 및 청색 반도체 발광 소자(R) 발광 소자에 의하여 적색(Red), 녹색(Green) 및 청색(Blue)의 단위 화소들이 하나의 화소(pixel)를 이루며, 이를 통하여 풀 칼라 디스플레이가 구현될 수 있다.

- [0084] 도 5b를 참조하면, 반도체 발광 소자(150a)는 황색 형광체층이 개별 소자 마다 구비된 백색 발광 소자(W)를 구비할 수 있다. 이 경우에는, 단위 화소를 이루기 위하여, 백색 발광 소자(W) 상에 적색 형광체층(181), 녹색 형광체층(182), 및 청색 형광체층(183)이 구비될 수 있다. 또한, 이러한 백색 발광 소자(W) 상에 적색, 녹색, 및 청색이 반복되는 컬러 필터를 이용하여 단위 화소를 이룰 수 있다.

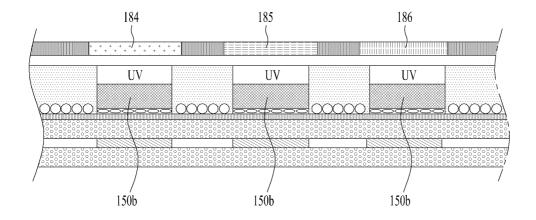

- [0085] 도 5c를 참조하면, 자외선 발광 소자(150b) 상에 적색 형광체층(184), 녹색 형광체층(185), 및 청색 형광체층 (186)이 구비되는 구조도 가능하다. 이와 같이, 반도체 발광 소자는 가시광선뿐만 아니라 자외선(UV)까지 전 영역에 사용 가능하며, 자외선(UV)이 상부 형광체의 여기원(excitation source)으로 사용 가능한 반도체 발광 소자의 형태로 확장될 수 있다.

- [0086] 본 예시를 다시 살펴보면, 반도체 발광 소자는 전도성 접착층 상에 위치되어, 디스플레이 장치에서 단위 화소를 구성한다. 반도체 발광 소자는 휘도가 우수하므로, 작은 크기로도 개별 단위 화소를 구성할 수 있다.

- [0087] 이와 같은 개별 반도체 발광 소자(150)의 크기는 예를 들어, 한 변의 길이가 80년 이하일 수 있고, 직사각형 또는 정사각형 소자일 수 있다. 직사각형인 경우에는 20 X 80년 이하의 크기가 될 수 있다.

- [0088] 또한, 한 변의 길이가 10µm인 정사각형의 반도체 발광 소자(150)를 단위 화소로 이용하여도 디스플레이 장치를 이루기 위한 충분한 밝기가 나타난다.

- [0089] 따라서, 단위 화소의 크기가 한 변이 600μm, 나머지 한 변이 300μm인 직사각형 화소인 경우를 예로 들면, 반도 체 발광 소자의 거리가 상대적으로 충분히 크게 된다.

- [0090] 따라서, 이러한 경우, HD화질 이상의 고화질을 가지는 플렉서블 디스플레이 장치를 구현할 수 있게 된다.

- [0091] 상기에서 설명된 반도체 발광 소자를 이용한 디스플레이 장치는 새로운 형태의 제조방법에 의하여 제조될 수 있다. 이하, 도 6을 참조하여 상기 제조 방법에 대하여 설명한다.

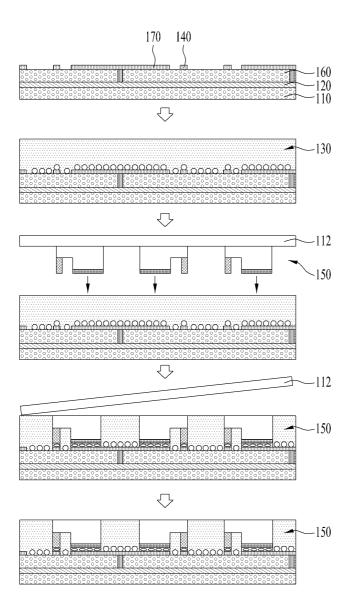

- [0092] 도 6은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 제조 방법을 나타낸 단면도들이다.

- [0093] 도 6에 도시된 바와 같이, 먼저, 보조전극(170) 및 제2전극(140)이 위치된 절연층(160) 상에 전도성 접착층 (130)을 형성한다. 배선기판(110)에 절연층(160)이 적층되며, 상기 배선기판(110)에는 제1전극(120), 보조전극 (170) 및 제2전극(140)이 배치된다. 이 경우에, 제1전극(120)과 제2전극(140)은 상호 직교 방향으로 배치될 수 있다. 또한, 플렉서블(flexible) 디스플레이 장치를 구현하기 위하여 배선기판(110) 및 절연층(160)은 각각 유리 또는 폴리이미드(PI)를 포함할 수 있다.

- [0094] 상기 전도성 접착층(130)은 예를 들어, 이방성 전도성 필름에 의하여 구현될 수 있으며, 이를 위하여 절연층 (160)이 위치된 기판에 이방성 전도성 필름이 도포될 수 있다.

- [0095] 다음에, 보조전극(170) 및 제2전극(140)들의 위치에 대응하고, 개별 화소를 구성하는 복수의 반도체 발광 소자 (150)가 위치된 임시기판(112)을, 상기 반도체 발광 소자(150)가 보조전극(170) 및 제2전극(140)와 마주하도록 배치한다.

- [0096] 이 경우에, 임시기판(112)은 반도체 발광 소자(150)를 성장시키는 성장 기판으로서, 사파이어(spire) 기판 또는 실리콘(silicon) 기판이 될 수 있다.

- [0097] 상기 반도체 발광 소자는 웨이퍼(wafer) 단위로 형성될 때, 디스플레이 장치를 이룰 수 있는 간격 및 크기를 가지도록 함으로써, 디스플레이 장치에 효과적으로 이용될 수 있다.

- [0098] 그 다음에, 배선기판과 임시기판(112)을 열 압착한다. 예를 들어, 배선기판과 임시기판(112)은 ACF 프레스 헤드를 적용하여 열 압착할 수 있다. 상기 열 압착에 의하여 배선기판과 임시기판(112)은 본딩(bonding)된다. 열 압착에 의하여 전도성을 갖는 이방성 전도성 필름의 특성에 의해 반도체 발광 소자(150)와 보조전극(170) 및 제2전극(140)의 사이의 부분만 전도성을 가지게 되며, 이를 통하여 전극들과 반도체 발광 소자(150)는 전기적으로 연결될 수 있다. 이 때에, 반도체 발광 소자(150)가 상기 이방성 전도성 필름의 내부로 삽입되며, 이를 통하여 반도체 발광 소자(150) 사이에 격벽이 형성될 수 있다.

- [0099] 그 다음에, 상기 임시기판(112)을 제거한다. 예를 들어, 임시기판(112)은 레이저 리프트 오프법(Laser Lift-off, LLO) 또는 화학적 리프트 오프법(Chemical Lift-off, CLO)을 이용하여 제거할 수 있다.

- [0100] 마지막으로, 상기 임시기판(112)을 제거하여 반도체 발광 소자들(150)을 외부로 노출시킨다. 필요에 따라, 반도체 발광 소자(150)가 결합된 배선기판 상을 실리콘 옥사이드(SiOx) 등을 코팅하여 투명 절연충(미도시)을 형성할 수 있다.

- [0101] 또한, 상기 반도체 발광 소자(150)의 일 면에 형광체층을 형성하는 단계를 더 포함할 수 있다. 예를 들어, 반도체 발광 소자(150)는 청색(B) 광을 발광하는 청색 반도체 발광 소자고, 이러한 청색(B) 광을 단위 화소의 색상으로 변환시키기 위한 적색 형광체 또는 녹색 형광체가 상기 청색 반도체 발광 소자의 일면에 레이어를 형성할수 있다.

- [0102] 이상에서 설명된 반도체 발광 소자를 이용한 디스플레이 장치의 제조 방법이나 구조는 여러 가지 형태로 변형될 수 있다. 그 예로서, 상기에서 설명된 디스플레이 장치에는 수직형 반도체 발광 소자도 적용될 수 있다.

- [0103] 또한, 이하 설명되는 변형예 또는 실시예에서는 앞선 예와 동일 또는 유사한 구성에 대해서는 동일, 유사한 참 조번호가 부여되고, 그 설명은 처음 설명으로 갈음된다.

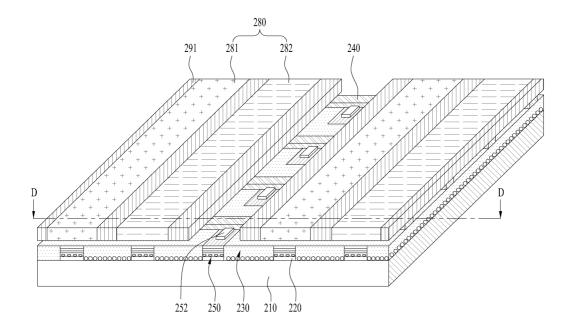

- [0104] 도 7은 본 발명의 반도체 발광 소자를 이용한 디스플레이 장치의 다른 일 실시예를 나타내는 사시도이고, 도 8은 도 7의 라인 D-D를 따라 취한 단면도이며, 도 9은 도 8의 수직형 반도체 발광 소자를 나타내는 개념도이다.

- [0105] 본 도면들을 참조하면, 디스플레이 장치는 패시브 매트릭스(Passive Matrix, PM) 방식의 수직형 반도체 발광 소자를 이용한 디스플레이 장치가 될 수 있다.

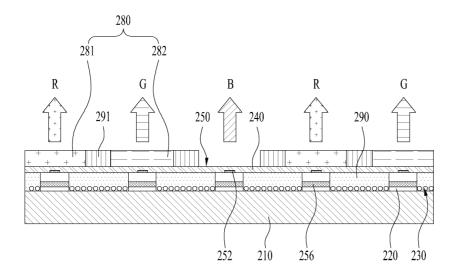

- [0106] 상기 디스플레이 장치는 기판(210), 제1전극(220), 전도성 접착충(230), 제2전극(240) 및 적어도 하나의 반도체 발광 소자(250)를 포함한다.

- [0107] 기판(210)은 제1전극(220)이 배치되는 배선기판으로서, 플렉서블(flexible) 디스플레이 장치를 구현하기 위하여 폴리이미드(PI)를 포함할 수 있다. 이외에도 절연성이 있고, 유연성 있는 재질이면 어느 것이라도 사용 가능할

것이다.

- [0108] 제1전극(220)은 기판(210) 상에 위치하며, 일 방향으로 긴 바(bar) 형태의 전극으로 형성될 수 있다. 상기 제1 전극(220)은 데이터 전극의 역할을 하도록 이루어질 수 있다.

- [0109] 전도성 접착층(230)은 제1전극(220)이 위치하는 기판(210)상에 형성된다. 플립 칩 타입(flip chip type)의 발광소자가 적용된 디스플레이 장치와 같이, 전도성 접착층(230)은 이방성 전도성 필름(Anisotropy Conductive Film, ACF), 이방성 전도 페이스트(paste), 전도성 입자를 함유한 솔루션(solution) 등이 될 수 있다. 다만, 본실시 예에서도 이방성 전도성 필름에 의하여 전도성 접착층(230)이 구현되는 경우를 예시한다.

- [0110] 기판(210) 상에 제1전극(220)이 위치하는 상태에서 이방성 전도성 필름을 위치시킨 후에, 반도체 발광 소자 (250)를 열 및 압력을 가하여 접속시키면, 상기 반도체 발광 소자(250)가 제1전극(220)과 전기적으로 연결된다. 이 때, 상기 반도체 발광 소자(250)는 제1전극(220) 상에 위치되도록 배치되는 것이 바람직하다.

- [0111] 상기 전기적 연결은 전술한 바와 같이, 이방성 전도성 필름에서 열 및 압력이 가해지면 부분적으로 두꼐방향으로 전도성을 가지기 때문에 생성된다. 따라서, 이방성 전도성 필름에서는 두께 방향으로 전도성을 가지는 부분과 전도성을 가지지 않는 부분으로 구획된다.

- [0112] 또한, 이방성 전도성 필름은 접착 성분을 함유하기 때문에, 전도성 접착층(230)은 반도체 발광 소자(250)와 제1 전극(220) 사이에서 전기적 연결뿐만 아니라 기계적 결합까지 구현한다.

- [0113] 이와 같이, 반도체 발광 소자(250)는 전도성 접착층(230) 상에 위치되며, 이를 통하여 디스플레이 장치에서 개별 화소를 구성한다. 반도체 발광 소자(250)는 휘도가 우수하므로, 작은 크기로도 개별 단위 픽셀을 구성할 수 있다. 이와 같은 개별 반도체 발광 소자(250)의 크기는 예를 들어, 한 변의 길이가 80㎞ 이하일 수 있고, 직사각형 또는 정사각형 소자일 수 있다. 직사각형인 경우에는 예를 들어, 20 X 80㎞ 이하의 크기가 될 수 있다.

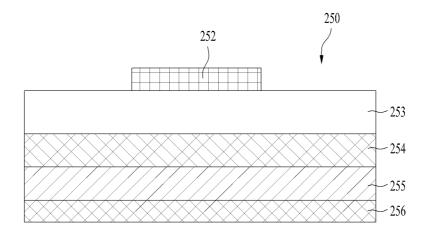

- [0114] 상기 반도체 발광 소자(250)는 수직형 구조가 될 수 있다.

- [0115] 수직형 반도체 발광 소자들의 사이에는, 제1전극(220)의 길이 방향과 교차하는 방향으로 배치되고, 수직형 반도 체 발광 소자(250)와 전기적으로 연결된 복수의 제2전극(240)이 위치한다.

- [0116] 도 9를 참조하면, 이러한 수직형 반도체 발광 소자(250)는 p형 전극(256), p형 전극(256) 상에 형성된 p형 반도 체충(255), p형 반도체충(255) 상에 형성된 활성충(254), 활성충(254)상에 형성된 n형 반도체충(253) 및 n형 반도체충(253) 상에 형성된 n형 전극(252)을 포함한다. 이 경우, 하부에 위치한 p형 전극(256)은 제1전극(220)과 전도성 접착충(230)에 의하여 전기적으로 연결될 수 있고, 상부에 위치한 n형 전극(252)은 후술하는 제2전극(240)과 전기적으로 연결될 수 있다. 이러한 수직형 반도체 발광 소자(250)는 전극을 상/하로 배치할 수 있으므로, 칩 사이즈를 줄일 수 있다는 큰 강점을 가지고 있다.

- [0117] 다시 도 8을 참조하면, 상기 반도체 발광 소자(250)의 일면에는 형광체층(280)이 형성될 수 있다. 예를 들어, 반도체 발광 소자(250)는 청색(B) 광을 발광하는 청색 반도체 발광 소자(251)이고, 이러한 청색(B) 광을 단위 화소의 색상으로 변환시키기 위한 형광체층(280)이 구비될 수 있다. 이 경우에, 형광체층(280)은 개별 화소를 구성하는 적색 형광체(281) 및 녹색 형광체(282) 일 수 있다.

- [0118] 즉, 적색의 단위 화소를 이루는 위치에서, 청색 반도체 발광 소자 상에는 청색 광을 적색(R) 광으로 변환시킬수 있는 적색 형광체(281)가 적충될 수 있고, 녹색의 단위 화소를 이루는 위치에서는, 청색 반도체 발광 소자 상에 청색광을 녹색(G) 광으로 변환시킬 수 있는 녹색 형광체(282)가 적충될 수 있다. 또한, 청색의 단위 화소를 이루는 부분에는 청색 반도체 발광 소자만 단독으로 이용될 수 있다. 이 경우, 적색(R), 녹색(G), 및 청색(B)의 단위 화소들이 하나의 화소를 이룰 수 있다.

- [0119] 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 플립 칩 타입(flip chip type)의 발광 소자가 적용된 디스 플레이 장치에서 전술한 바와 같이, 청색, 적색, 녹색을 구현하기 위한 다른 구조가 적용될 수 있다.

- [0120] 다시 본 실시예를 살펴보면, 제2전극(240)은 반도체 발광 소자들(250) 사이에 위치하고, 반도체 발광 소자들 (250)과 전기적으로 연결된다. 예를 들어, 반도체 발광 소자들(250)은 복수의 열로 배치되고, 제2전극(240)은 반도체 발광 소자들(250)의 열들 사이에 위치할 수 있다.

- [0121] 개별 화소를 이루는 반도체 발광 소자(250) 사이의 거리가 충분히 크기 때문에 제2전극(240)은 반도체 발광 소자들(250) 사이에 위치될 수 있다.

- [0122] 제2전극(240)은 일 방향으로 긴 바(bar) 형태의 전극으로 형성될 수 있으며, 제1전극과 상호 수직한 방향으로 배치될 수 있다.

- [0123] 또한, 제2전극(240)과 반도체 발광 소자(250)는 제2전극(240)에서 돌출된 연결 전극에 의해 전기적으로 연결될수 있다. 보다 구체적으로, 상기 연결 전극이 반도체 발광 소자(250)의 n형 전극이 될 수 있다. 예를 들어, n형 전극은 오믹(ohmic) 접촉을 위한 오믹 전극으로 형성되며, 상기 제2전극은 인쇄 또는 증착에 의하여 오믹 전극의 적어도 일부를 덮게 된다. 이를 통하여 제2전극(240)과 반도체 발광 소자(250)의 n형 전극이 전기적으로 연결될 수 있다.

- [0124] 다시 도 8을 참조하면, 상기 제2전극(240)은 전도성 접착층(230) 상에 위치될 수 있다. 경우에 따라, 반도체 발광 소자(250)가 형성된 기판(210) 상에 실리콘 옥사이드(SiOx) 등을 포함하는 투명 절연층(미도시)이 형성될 수있다. 투명 절연층이 형성된 후에 제2전극(240)을 위치시킬 경우, 상기 제2전극(240)은 투명 절연층 상에 위치하게 된다. 또한, 제2전극(240)은 전도성 접착층(230) 또는 투명 절연층에 이격되어 형성될 수도 있다.

- [0125] 만약 반도체 발광 소자(250) 상에 제2전극(240)을 위치시키기 위하여는 ITO(Indium Tin Oxide)와 같은 투명 전 극을 사용한다면, ITO 물질은 n형 반도체층과는 접착성이 좋지 않은 문제가 있다. 따라서, 본 발명은 반도체 발광 소자(250) 사이에 제2전극(240)을 위치시킴으로써, ITO와 같은 투명 전극을 사용하지 않아도 되는 이점이 있다. 따라서, 투명한 재료 선택에 구속되지 않고, n형 반도체층과 접착성이 좋은 전도성 물질을 수평 전극으로 사용하여 광추출 효율을 향상시킬 수 있다.

- [0126] 다시 도 8을 참조하면, 반도체 발광 소자(250) 사이에는 격벽(290)이 위치할 수 있다. 즉, 개별 화소를 이루는 반도체 발광 소자(250)를 격리시키기 위하여 수직형 반도체 발광 소자(250) 사이에는 격벽(290)이 배치될 수 있다. 이 경우, 격벽(290)은 개별 단위 화소를 서로 분리하는 역할을 할 수 있으며, 상기 전도성 접착층(230)과 일체로 형성될 수 있다. 예를 들어, 이방성 전도성 필름에 반도체 발광 소자(250)가 삽입됨에 의하여 이방성 전도성 필름의 베이스부재가 상기 격벽을 형성할 수 있다.

- [0127] 또한, 상기 이방성 전도성 필름의 베이스 부재가 블랙이면, 별도의 블랙 절연체가 없어도 상기 격벽(290)이 반사 특성을 가지는 동시에 대비비(contrast)가 증가될 수 있다.

- [0128] 다른 예로서, 상기 격벽(190)으로서, 반사성 격벽이 별도로 구비될 수 있다. 격벽(290)은 디스플레이 장치의 목 적에 따라 블랙(Black) 또는 화이트(White) 절연체를 포함할 수 있다.

- [0129] 만일 제2전극(240)이 반도체 발광 소자(250) 사이의 전도성 접착층(230) 상에 바로 위치된 경우, 격벽(290)은 수직형 반도체 발광 소자(250) 및 제2전극(240)의 사이 사이에 위치될 수 있다. 따라서, 반도체 발광 소자(250)를 이용하여 작은 크기로도 개별 단위 픽셀을 구성할 수 있고, 반도체 발광 소자(250)의 거리가 상대적으로 충분히 크게 되어 제2전극(240)을 반도체 발광 소자(250) 사이에 위치시킬 수 있고, HD 화질을 가지는 플랙서블 디스플레이 장치를 구현할 수 있는 효과가 있게 된다.

- [0130] 또한, 도8에 도시된 바와 같이, 대비비(contrast) 향상을 위하여 각각의 형광체 사이에는 블랙 매트릭스(291)가 배치될 수 있다. 즉, 이러한 블랙 매트릭스(291)는 명암의 대조를 향상시킬 수 있다.

- [0131] 전술하였듯이, 반도체 발광 소자를 이용한 대화면 고화소 디스플레이 장치의 경우, 성장 기판에서 성장한 상기 반도체 발광 소자는 새로운 기판으로 조립되거나 전사되어야 한다. 상기 성장 기판은 예를 들어, 8인치 웨이퍼 일 수 있으며, 이에 따라서 복수 번의 전사가 반복될 수 있다.

- [0132] 상기 조립 또는 전사 과정은 예를 들어, 매우 많은 수의 반도체 발광 소자가 일괄적으로 새로운 기판에 배열되는 과정이며, 상기 배열 과정에서 설정된 위치와 다른 위치로 배열될 수 있어, 배열 오차가 존재하게 된다.

- [0133] 또한, 상기 조립 또는 전사 이후, 상기 반도체 발광 소자를 전기적으로 연결하기 위한 배선 공정이 수행되며, 상기 배열 오차의 범위가 일정한 스펙(Spec) 범위를 초과하는 경우, 상기 반도체 발광 소자는 쇼트(short) 또는 오픈(open) 불량을 유발하게 된다.

- [0134] 따라서 상기 배선 공정 상 불량의 위험을 최소화하고, 안정적으로 소자를 전사하기 위한 방법으로, 반도체 발광소자 영역에만 선택적으로 이방 전도성 접착 페이스트층이 형성되는 (Anisotropy Conductive adhesive paste; ACP) 디스플레이 장치 및 제조 방법에 대해 이하 도 10 내지 도 23에서 상세히 후술하도록 하겠다.

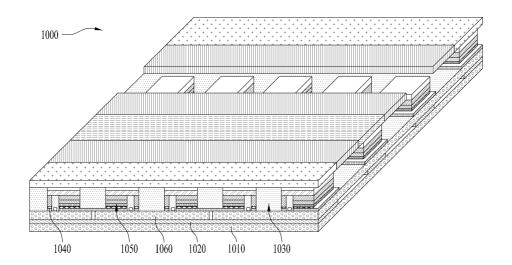

- [0135] 도 10에 도시된 바와 같이, 반도체 발광 소자를 이용한 디스플레이 장치(1000)로서, 패시브 매트릭스(Passive Matrix, PM) 방식의 플립 칩 반도체 발광 소자(1050)를 이용한 디스플레이 장치(1000)를 예시한다. 다만, 이하

설명되는 예시는 액티브 매트릭스(Active Matrix, AM) 방식의 반도체 발광 소자에도 적용 가능하다. 또한 상기 반도체 발광 소자(1050)의 기술적 특징은 소자의 전극부 및 그 주변부에 선택적으로 형성되는 이방 전도성 접착 페이스트층 및, 불규칙한 요철 구조의 배선 전극인 바, 상기 플립 칩 구조는 예시적인 사항일 뿐, 본 발명이 이에 한정되는 것은 아니다.

- [0136] 디스플레이 장치(1000)는 배선 기판(1010), 제1전극(1020), 절연층(1030), 제2전극(1040) 및 복수의 반도체 발광 소자(1050)를 포함한다. 여기에서, 제1 전극(1020) 및 제2 전극(1040)은 각각 복수의 전극 라인을 포함할 수있다.

- [0137] 또한, 배선 기판(1010)은, 플렉서블(flexible) 디스플레이 장치를 구현하기 위하여 폴리이미드(PI)를 포함할 수 있다. 이외에도 예를 들어, 절연성이 있고, 유연성 있는 재질이면 어느 것이라도 사용 가능하다.

- [0138] 상기 제1전극(1020) 및 상기 제 2전극(1040)은 배선 기판(1010) 상에 위치하며, 상기 반도체 발광 소자(1050)의 도전형 전극과 전기적으로 연결되도록 배치될 수 있다.

- [0139] 상기 반도체 발광 소자(1050)들의 사이에는, 제1전극(1020)의 길이 방향과 교차하는 방향으로 배치되고, 상기 반도체 발광 소자(1050)와 전기적으로 연결된 복수의 제2전극(1040)이 위치한다.

- [0140] 또한, 도 10에 도시된 바와 같이, 복수의 반도체 발광소자(1050)는 제1전극(1020)에 구비되는 복수의 전극 라인 들과 나란한 방향으로 복수의 열들을 형성할 수 있다. 다만, 본 발명은 이에 한정되는 것은 아니다. 예를 들어, 복수의 반도체 발광 소자(1050)는 제2전극(1040)을 따라 복수의 열들을 형성할 수 있다.

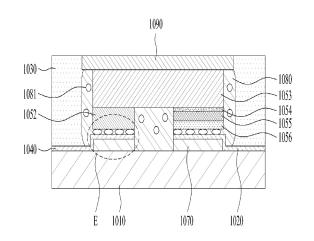

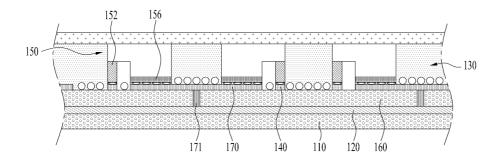

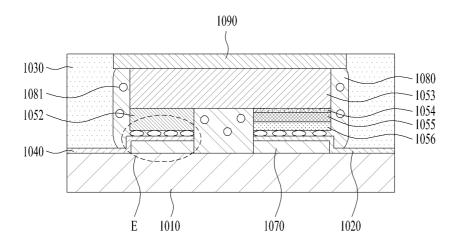

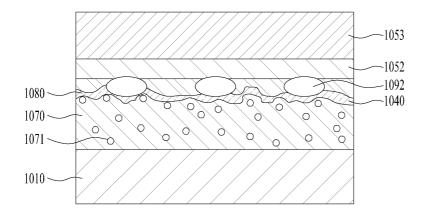

- [0141] 도 11은 도 10의 반도체 발광 소자 및 상기 반도체 발광 소자와 연결되는 배선 전극을 구체적으로 나타내는 도 면이다.

- [0142] 상기 반도체 발광 소자(1050)는 제 1도전형 반도체층(1055), 활성층(1054), 제 2도전형 반도체층(1053)을 포함 할 수 있다.

- [0143] 또한, 상기 제 1도전형 반도체층(1055)과 전기적으로 연결되는 제 1도전형 전극(1056) 및 상기 제 2도전형 반도 체층(1053)과 전기적으로 연결되는 제 2도전형 전극(1052)을 더 포함할 수 있다.

- [0144] 또한, 상기 반도체 발광 소자의 제 2도전형 반도체충(1053)의 상측면은 보호충(1090)이 위치한다. 상기 보호충 (1090)은 고내열성 보호충으로 도 16 및 도 20에서 후술하겠지만, 임시 기판에서 배선 기판으로 반도체 발광 소자를 전사하는 경우, 상기 보호충(1090)과 오버랩되는 영역에 형성되는 이방 전도성 접착 페이스트충(1080)만 선택적으로 상기 반도체 발광 소자와 함께 전사할 수 있도록 그 역할을 한다.

- [0145] 따라서, 도 11에 도시된 바와 같이, 상기 보호층(1090)의 하부에 배치된 반도체 발광 소자의 측면 및 하면에는 이방 전도성 접착 페이스트층(1080)이 위치한다. 한편, 상기 이방 전도성 접착 페이스트층(1080)은 임시 기판에서 상기 반도체 발광 소자를 분리하는 과정에서, 그 분리 조건에 따라 다양한 형상으로 분리되어 상기 반도체 발광 소자의 주변부에 위치할 수 있다. 따라서 본 발명이 도 11에 도시된 형상으로 한정되는 것은 아니다.

- [0146] 또한, 도 11에 도시된 상기 보호층(1090)은 제 2도전형 반도체층(1053)보다 양측면 방향으로 더 돌출되어 있으나, 이는 일 예시에 불과하며, 상기 반도체 발광 소자의 전사 과정에서 다양하게 형성될 수 있다. 예를 들어, 상기 제 2도전형 반도체층(1053)과 동일한 길이를 가지는 보호층이 형성될 수 있으며, 제 2도전형 반도체층 (1053)의 일 측면보다 돌출되도록 형성할 수도 있다.

- [0147] 또한, 도 11에 도시된 바와 같이, 상기 배선 기판(1010)은 유기물 패드(1070), 상기 유기물 패드(1070)의 상부에 위치한 제 1전극(1020) 및 제 2전극(1040)을 포함한다.

- [0148] 상기 제 1전극(1020)은 상기 반도체 발광 소자의 제 1도전형 전극(1056)과 상기 이방 전도성 접착 페이스트층 (1080)의 도전형 입자에 의해 전기적으로 연결된다. 또한, 상기 제 2전극(1040) 역시 상기 반도체 발광 소자의 제 2도전형 전극(1052)과 상기 이방 전도성 접착 페이스트층(1080)의 도전형 입자에 의해 전기적으로 연결된다.

- [0149] 상기 도전형 입자(1081)은 예를 들어, 원형의 형태로 상기 이방 전도성 접착 페이스트층(1080) 내에 존재하나, 상기 반도체 발광 소자가 배선 기판(1010)에 전사하는 과정에서, 압착에 의해 타원형으로 변형될 수 있다. 도 11에 도시된 바와 같이, 상기 제 1전극(1020)과 상기 제 1도전형 전극(1056) 사이에 존재하는 도전형 입자의 경우, 타원형의 형상을 지닌다.

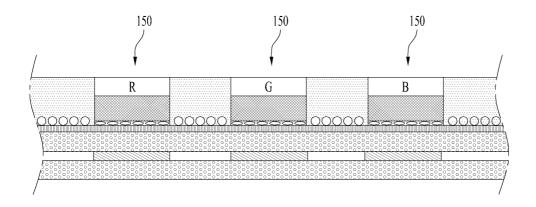

- [0150] 도 12는 도 11의 E부분을 확대한 도면이다.

- [0151] 상기 도 11의 E부분은 반도체 발광 소자의 제 2도전형 반도체층(1053)에 형성된 제 2도전형 전극(1052)과 제 2 전극(1040)의 연결 부위에 해당한다.

- [0152] 도 12에 도시된 바와 같이, 상기 제 2전극(1040)은 불규칙한 요철 구조를 구비한다. 상기 제 2전극(1040)은 배선 기판(1010)에 형성된 유기물 패드(1070)의 상부에 형성된다. 상기 유기물 패드(1070)는 복수의 나노 파티클 (1071)들을 포함하고, 적어도 하나 이상의 나노 파티클이 상기 유기물 패드(1070)의 표면 상 드러나는 구조를 가짐으로써 불규칙한 표면 형상을 형성한다.

- [0153] 추가적으로, 상기 나노 파티클들은 배선 기판과 도전성 입자의 접촉 시, 유기물 패드의 형상을 유지시키는 저항 체 역할을 하며, 디스플레이 장치 구동 시, 배선 기판으로 향하는 방출 광을 반사시켜 광추출 효율을 향상시키는 역할을 수행할 수 있다.

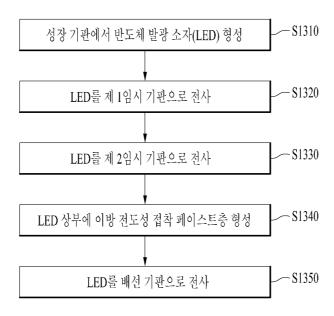

- [0154] 도 13은 도10의 디스플레이 장치를 제작하는 과정을 나타내는 순서도이다.

- [0155] 먼저, 성장 기판에서 반도체 발광 소자(LED)를 형성한다(S1310). 상기 반도체 발광 구조는 제 1도전형 반도체층, 활성층 및 제 2도전형 반도체층을 포함하고, 경우에 따라 버퍼 반도체층을 더 포함할 수 있다. 또한, 수평형 구조의 반도체 발광 소자의 경우, 상기 성장 기판에서 각 반도체층을 전기적으로 연결하기 위한 전극 형성이 진행된다.

- [0156] 이후, 상기 반도체 발광 소자(LED)를 제 1임시 기판으로 전사한다(S1320). 상기 제 1임시 기판은 예를 들어, PDMS와 같은 유연소재로 이루어질 수 있고, 복수 개의 돌기부를 구비할 수 있다.

- [0157] 또한, 상기 전사 단계(S1320)는 상기 반도체 발광 소자와 상기 돌기부가 오버랩되도록, 상기 성장 기판과 상기 제 1임시 기판을 얼라인(Align) 시키는 단계를 포함할 수 있다.

- [0158] 또한, 성장 기판에서 성장한 반도체 발광 소자가 제 1임시 기판으로 직접 전사될 수 있으나, 경우에 따라서, 별도의 조립 기판에서 조립된 반도체 발광 소자가 상기 제 1임시 기판으로 전사될 수 있다. 이 경우 상기 조립 기판의 반도체 발광 소자는 전자기장을 이용하여 유체 내에서 자가조립을 진행한 반도체 발광 소자일 수 있다. 따라서 도 11에서 언급하는 공정 순서는 본 발명의 기술적 특징을 드러내기 위한 예시적인 구성이며, 본 발명이 반드시 이에 한정하는 것은 아니다.

- [0159] 제 1임시 기판으로 전사된 반도체 발광 소자(LED)는 다시 제 2임시 기판으로 전사된다(S1330). 상기 제 2임시 기판에는 반도체 발광 소자의 선택적 전사를 위한 보호층 및 릴리즈층을 포함한다.

- [0160] 임시 기판을 이용하여 두 번의 전사 과정을 수행하는 이유는, 상기 반도체 발광 소자의 특정 면과 상기 보호층을 접촉시키기 위함이다.

- [0161] 예를 들어, 수평형 반도체 발광 소자는 상기 반도체 발광 소자의 한 쪽 방향으로만 도전형 전극이 형성된다. 즉, 성장 기판과 맞닿는 반도체 발광 소자의 면을 1면이라고 가정할 때, 반대되는 2면 상에 도전형 전극이 형성된다. 상기 보호층은 도전형 전극이 형성되지 않은 면과 접촉하는 것이 바람직한 바, 상기 1면과 상기 보호층을 접촉시키기 위해서는 두 번의 전사 과정이 필요하다.

- [0162] 다만, 반도체 발광 소자에서 도전형 전극이 형성되는 방향 및 그 밖의 목적에 따라 임시 기판의 전사 횟수는 추가될 수 있다.

- [0163] 이후, 제 2임시 기판에 전사된 상기 반도체 발광 소자(LED)의 상부에 이방 전도성 접착 페이스트층을 형성한다 (S1340).

- [0164] 마지막으로, 상기 이방 전도성 접착 페이스트층이 형성된 반도체 발광 소자를 배선 기판으로 전사한다(S1350).

- [0165] 상기 전사 단계에서는 상기 제 2임시 기판의 후면부에 레이저를 조사하여, 제 2임시 기판 상에 형성된 보호층과 더불어 반도체 발광 소자를 분리하는 과정이 포함되며, 이에 대한 상세한 내용은 도 18 및 도 19에서 후술한다.

- [0166] 한편, 본 명세서의 전 취지에 비추어 보아, 당업자가 이해 가능한 수준에서, 도 13에 도시된 순서도의 일부 단계를 삭제, 변경하는 것도 본 발명의 다른 권리범위에 속한다.

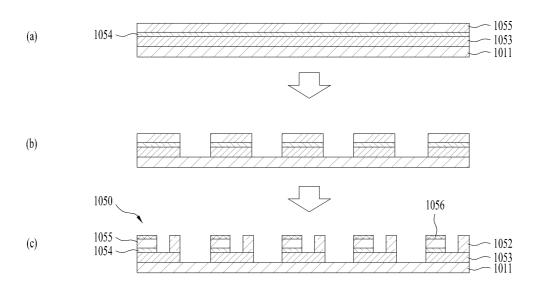

- [0167] 도 14는 도 10의 반도체 발광 소자를 성장 기판에서 형성하는 과정을 나타내는 단면도들이다.

- [0168] 도 14(a)에 도시된 바와 같이, 성장 기판(1011)에 제2도전형 반도체층(1053), 활성층(1054), 제1 도전형 반도체 층(1055)을 차례대로 성장시킨다.

- [0169] 추가적으로, 버퍼 반도체층이 제 2도전형 반도체층(1053)과 상기 성장 기판(1011) 사이에 형성될 수 있다. 상기 버퍼 반도체층은 상기 성장 기판(1011)에서 성장한 반도체 발광 소자를 분리하는 과정에서 발생할 수 있는 제 2 도전형 반도체층(1053)의 파손을 미연에 방지할 수 있다.

- [0170] 한편, 성장 기판(1011)은 광 투과적 성질을 가지는 재질, 예를 들어 사파이어(Al203), GaN, ZnO, Al0 중 어느하나를 포함하여 형성될 수 있다. 또한, 성장 기판(1011)은 반도체 물질 성장에 적합한 물질, 캐리어 웨이퍼로 형성될 수 있다. 성장 기판(1011)은 열 전도성이 뛰어난 물질로 형성될 수 있으며, 전도성 기판 또는 절연성 기판을 포함하여 예를 들어, 사파이어(Al203) 기판에 비해 열전도성이 큰 SiC 기판 또는 Si, GaAs, GaP, InP, Ga203 중 적어도 하나를 사용할 수 있으나, 이에 한정하지 않는다.

- [0171] 나아가, 제2도전형 반도체층(1053)은 n형 반도체층으로서, n-GaN 과 같은 질화물 반도체층이 될 수 있으며, 제1 도전형 반도체층(1055)은 p형 반도체층이 될 수 있다. 다만, 본 발명은 반드시 이에 한정되는 것은 아니며, 제1 도전형이 n형이 되고 제2도전형이 p형이 되는 예시도 가능하다.

- [0172] 또한, 본 발명의 다른 실시예에 따르면, 진성 또는 도핑된 반도체 기판에 불순물을 주입하여, 상기 제1도전형 반도체층(1055) 및 제2도전형 반도체층(1053)을 형성할 수 있다. 또한, 상기 불순물 주입에 의하여 p-n 접합이 형성된 영역이 상기 활성층(1053)과 같은 역할을 할 수도 있다. 상기 제1도전형 반도체층(1055), 제2도전형 반도체층(1053) 및 활성층(11054)에 대한 열거 사항은 예시적일 뿐 본 발명이 이에 한정되는 것은 아니다.

- [0173] 도 14(b)에 도시된 바에 같이, 성장 기판 상에서 성장한 반도체층은 식각 공정을 통해 서로 고립(isolation)된 복수의 반도체 발광 구조를 형성한다.

- [0174] 예를 들어, 상기 제1도전형 반도체층, 활성층, 제2도전형 반도체층 및 버퍼 반도체층의 적어도 일부를 식각하여, 상기 기판상에서 서로 고립(isolation)된 복수의 반도체 발광 구조를 형성한다. 이 경우에, 상기 식 각은 성장 기판이 드러날 때까지 진행될 수 있다.

- [0175] 다른 예로서, 반도체 발광 소자의 사이에서 상기 제2도전형 반도체층의 일부를 남겨놓은 상태까지 식각이 진행될 수도 있다.

- [0176] 도 14(c)에 도시된 바와 같이, 복수의 반도체 발광 소자(1050)의 상부에 제 1도전형 전극(1056) 및 제 2도전형 전극(1052)이 형성될 수 있다. 상기 전극들(1052, 1056)을 형성하기 위해서는 포토공정, 식각공정 및 메탈 증착 공정이 각 전극 별로 수행될 수 있다. 예를 들어, 수평형 반도체 발광 소자의 경우, 따라서 최종적으로 상기 성장 기판(1011) 위에는 제1도전형 전극(1056), 제 2도전형 전극(1052), 제 1도전형 반도체층(1055), 활성층 (1054), 제 2도전형 반도체층(1053)이 형성된 복수의 반도체 발광 소자(1050)가 형성될 수 있다. 또한, 상기 반도체 발광 소자(1050)는 예를 들어, 반도체 발광 소자(1050)의 측면을 감싸도록 형성되는 패시베이션층을 더 포함할 수 있다.

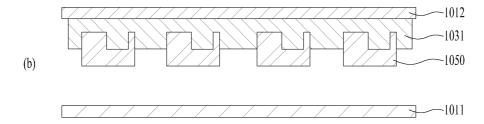

- [0177] 도 15는 도14의 반도체 발광 소자를 제 1임시 기판으로 전사하는 과정을 나타내는 도면들이다.

- [0178] 도 15(a)에서 도시하는 바와 같이, 제 1임시 기판(1012)상에 형성된 접착 필름(1031)을 통해 성장 기판(1011)의 반도체 발광 소자(1050)가 제 1임시 기판(1012)으로 전사될 수 있다.

- [0179] 상기 전사 과정 중에는, 성장 기판(1011)의 반도체 발광 소자(1050)를 선택적으로 분리하기 위해 레이저 리프트 오프(laser lift off; LLO) 과정이 수행될 수 있다. 즉, 성장 기판(1011) 측에서 분리하고자 하는 반도체 발광 소자(1050)에 레이저를 조사하면 성장 기판(1011)과 해당 반도체 발광 소자(1050)는 분리될 수 있다. 제 1임시 기판(1012)의 접착 필름(1031)은 선택적 전사에 적합한 유연 필름일 수 있다.

- [0180] 따라서, 도 15(b)에 도시된 바와 같이, 성장 기판(1011)에서 분리된 반도체 발광 소자(1050)의 경우, 제 1임시 기판(1012)의 접착 필름(1031)에 모두 접착될 수 있다. 상기 접착 필름(1031)은 유연성이 있어, 상기 반도체 발광 소자(1050)는 안정적으로 상기 접착 필름(1031) 상에 고정되게 된다.

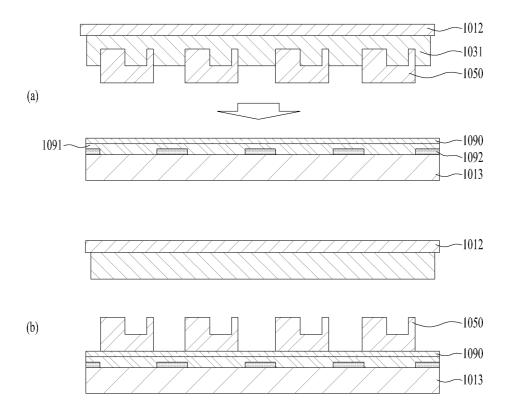

- [0181] 도 16은 도15의 반도체 발광 소자를 제 2임시 기판으로 전사하는 과정을 나타내는 도면들이다.

- [0182] 도 16(a)에 도시된 바와 같이, 상기 제 2임시 기판(1013)은 보호층(1090), 보호층 하부에 형성된 릴리즈층 (1091) 및 릴리즈(Release) 레이저 반사층(1092)을 구비한다.

- [0183] 제 2임시 기판(1013)으로 상기 반도체 발광 소자(1050)을 전사하기 위해, 제 1임시 기판(1012)과 제 2임시 기판 (1013)을 압착한 후 분리한다.

- [0184] 상기 제 2임시 기판(1013)의 상기 보호층(1090)은 접착성분을 포함하고, 상기 접착성분에 의한 접착력은 제 1임시 기판(1012)의 접착 필름(1031)의 접착력보다 강한 것을 특징으로 한다. 따라서 도 16(b)에 도시된 바와 같이, 반도체 발광 소자(1050)는 제 1임시 기판(1012)에서 제 2임시 기판(1013)의 보호층(1090)으로 안정적으로 분리될 수 있다.

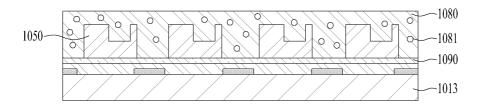

- [0185] 도 17은 도16의 제 2임시 기판 상의 반도체 발광 소자에 이방 전도성 접착 페이스트층을 형성한 이후의 단면도 이다.

- [0186] 도 17에 도시된 바와 같이, 상기 제 2임시 기판(1013)의 보호층(1090) 상부에 위치한 반도체 발광 소자(1050)에 대해, 도전성 입자(1081)를 함유한 이방 전도성 접착 페이스트층(1080)를 코팅된다.

- [0187] 상기 이방 전도성 접착 페이스트층(1080)를 코팅하기 위해, 스핀 코팅(spin coating), 바 코팅(bar coating) 및 슬릿 코팅(slit coating) 등 다양한 방법 중 하나를 선택할 수 있다.

- [0188] 또한 상기 이방 전도성 접착 페이스트층(1080)은 반도체 발광 소자의 휘도 개선을 위한 TiO2 나노 파티클 또는 코팅 특성 향상을 위한 실리카 재질의 나노 파티클을 포함할 수 있다.

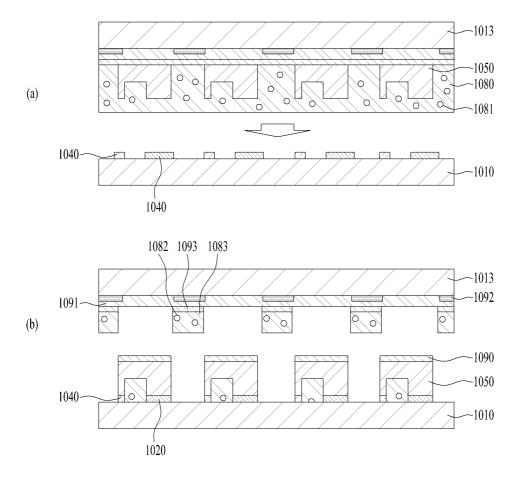

- [0189] 도 18은 도17의 반도체 발광 소자를 배선 기판으로 전사하는 과정을 나타내는 도면들이다.

- [0190] 도 18(a)에 도시된 바와 같이, 제 2임시 기판(1013) 상에 위치하는 반도체 발광 소자(1050)는 배선 기판(1010) 과 마주보도록 뒤집어서 전사한다. 즉, 상기 반도체 발광 소자(1050) 상에 코팅된 도전성 입자(1081)를 포함한 이방 전도성 접착 페이스트층(1080)이 상기 배선 기판(1010) 상에 형성된 제 1전극(1020) 및 제 2전극(1040)과 접촉할 수 있도록 위치시킨다.

- [0191] 이후, 상기 제 2임시 기판(1013)과 상기 배선 기판(1010)을 압착하고, 상기 제 2임시 기판(1013)의 후면부에 레이저를 조사하여, 상기 제 2임시 기판 상에 기 형성된 보호층과 릴리즈층(Release layer) 사이를 분리시킨다.

- [0192] 도 18(b)는 상기 제 2임시 기판(1013)에서 상기 배선 기판(1010)으로 상기 반도체 발광 소자(1050)가 전사된 이후의 형상을 도시한 도면이다.

- [0193] 상기 제 2임시 기판(1013)에는 릴리즈 레이저 반사층(1092) 및 릴리즈층(1091)은 그대로 위치하고 있으며, 일부 보호층(1093) 및 일부 도전성 입자(1082)를 포함한 이방 전도성 접착 페이스트층(1083)만이 잔존한다.

- [0194] 상기 보호층(1093) 및 도전성 입자(1082)를 포함한 이방 전도성 접착 페이스트층(1083)은 기존에 제 2임시 기판 (1013)에 위치했던 반도체 발광 소자들의 사이 영역에 존재하는 것들이다.

- [0195] 즉, 전사 과정에서, 반도체 발광 소자(1050) 상에 위치한 보호층(1090) 및 상기 반도체 발광 소자(1050)을 감싸는 이방 전도성 접착 페이스트층은 함께 배선 기판(1010)으로 전사된다.

- [0196] 도 18(b)에 도시된 바와 같이, 상기 배선 기판(1010) 상에는 제 1전극(1020) 및 제 2전극(1040)이 위치하고, 상기 전극들(1020,1040) 상에 반도체 발광 소자(1050)가 배치된다. 또한 상기 반도체 발광 소자(1050) 상측면에는 보호층(1090)이 존재한다. 또한, 상기 반도체 발광 소자(1050)의 측면 및, 상기 반도체 발광 소자(1050)과 상기 전극들(1020,1040) 사이에 이방 전도성 접착 페이스트층이 위치한다. 나아가, 상기 전극들(1020,1040)과 반도체 발광 소자(1050) 사이의 이방 전도성 접착 페이스트층은 전사과정 중 압착되고, 상기 이방 전도성 접착 페이스트층의 도전성 입자에 의해 상기 반도체 발광 소자(1050)과 전극들(1020,1040)을 전기적으로 연결시킨다.

- [0197] 중래, 이방 전도성 접착 필름(Anisotropic conductive adhesive film)를 사용하여 배선 전극과 반도체 발광 소자를 연결하는 경우, 상기 전도성 필름에 포함된 도전성 입자에 의해 반도체 발광 소자들간의 쇼트(short) 또는 오픈(Open)불량이 발생할 가능성이 농후했다. 즉, 도전성 입자의 농도가 미약한 경우, 상기 도전성 입자에 의한 전극 간의 전기적 연결이 어렵다는 단점이 있었다. 또한, 상기 도전성 입자가 과도한 경우, 상기 도전성 입자들이, 원하지 않은 영역, 예를 들어 소자와 소자의 사이에서도 하나의 배선처럼 형성되어 쇼트 불량을 유발하였다. 따라서 상기 도전성 입자의 농도를 조절하는 것은 중요한 문제였으나, 접착 압력 및 도전성 입자의 크기 등의 변수가 다양하여, 적절한 농도 지점을 설정하기 어려운 단점이 있었다.

- [0198] 하지만 본 발명의 경우, 이방 전도성 접착 페이스트층을 사용함과 동시에, 상기 이방 전도성 접착 페이스트층이 개별 반도체 발광 소자의 도전형 전극부 및 그 인근에만 선택적으로 형성되게 함으로써, 상기 도전성 입자에 따른 불량 문제를 최소화시킬 수 있다.

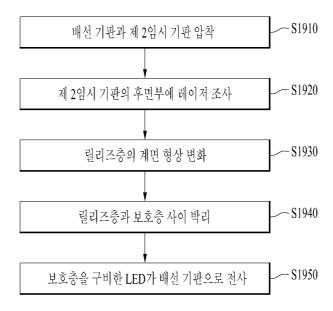

- [0199] 도 19은 도18의 반도체 발광 소자가 배선 기판으로 전사되는 과정을 구체적으로 나타내는 순서도이다.

- [0200] 도18에서 간략하게 전술하였듯이, 먼저 배선 기판과 제 2임시 기판을 마주보도록 배치하고 압착한다(S1910).

- [0201] 이후 제 2임시 기판의 후면부에 레이저를 조사한다(S1920). 상기 레이저는 UV(Ultra Violet) 또는 가시광 영역 대의 레이저일 수 있다. 상기 레이저의 진행 방향은 제 2임시 기판, 제 2임시 기판 상에 형성된 릴리즈 레이저 반사층 또는 릴리즈층의 순서이다. 상기 레이저가 릴리즈 레이저 반사층에 조사되면, 더 이상 상기 레이저는 직진하지 못하고 반사되어 상기 릴리즈 레이저 반스층 상부에 위치한 릴리즈층 및 보호층에는 영향을 주기 어렵다. 하지만 예를 들어, 릴리즈 레이저 반사층이 형성되지 않은 영역에서는 릴리즈층 및 릴리즈층의 상부에 형성된 보호층에 영향을 주게 된다.

- [0202] 상기 레이저에 의해, 상기 릴리즈층은 상기 레이저의 파장에 대응하는 에너지를 흡수하고 이에 따른 열이 발생한다. 따라서 상기 열에 의해 상기 릴리즈층의 계면 형상은 변화하게 된다(S1930).

- [0203] 한편, 상기 릴리즈층의 상부에 형성된 보호층의 경우 상기 레이저에 의해 발생된 열을 견딜 수 있는 고내열성 재료로 형성된다. 따라서 상기 레이저에 의해 상기 릴리즈층은 기화 등의 이유로 형상이 변하는 반면, 상기 보호층의 형상은 그대로 유지될 수 있다. 따라서 레이저가 조사되는 시간이 경과함에 따라, 상기 릴리즈층과 상기 보호층 사이는 박리된다(S1940).

- [0204] 한편, 상기 보호층과 반대면에 형성된, 상기 반도체 발광 소자의 도전형 전극 및 그 주변부에 위치하는 이방 전도성 접착 페이스트층은 상기 압착 단계(S1910)에서 배선 기판과 강하게 접촉하게 되고, 이에 따라 상기 배선 기판 및 상기 반도체 발광 소자 사이에서 강한 접착력을 유지한다.

- [0205] 따라서 배선 기판과 제 2임시 기판을 압착 후 분리하는 경우, 제 2임시 기판의 반도체 발광 소자는 상기 제 2임시 기판 상에 기 형성된 보호층과 함께 배선 기판으로 전사된다(S1950). 즉, 상기 반도체 발광 소자 및 상기 반도체 발광 소자와 오버랩되는 보호층만이 릴리즈층과의 계면 박리에 의해 함께 전사된다. 이는 제 2임시 기판에 상기 반도체 발광 소자가 위치하는 영역에는 릴리즈 레이저 반사층이 형성되지 않아 레이저에 의한 영향을 받은 결과이다. 다른 한편, 제 2임시 기판에 상기 반도체 발광 소자가 위치하지 않는 영역은 릴리즈 레이저 반사층을 구비하고, 이에 따라 레이저에 의한 영향을 받지 않아, 릴리즈층과 보호층의 박리가 발생하지 않는다. 상기 릴리즈층과 릴리즈 레이저 반사층의 형성과정 및 구조에 대한 보다 자세한 설명은 도 20에서 후술한다.

- [0206] 한편, 본 명세서의 전 취지에 비추어 보아, 당업자가 이해 가능한 수준에서, 도 19에 도시된 순서도의 일부 단계를 삭제, 변경하는 것도 본 발명의 다른 권리범위에 속한다.

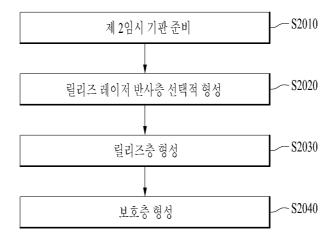

- [0207] 도 20은 반도체 발광 소자 및 이방 전도성 접착 페이스트층의 선택적 전사를 위해 제 2임시 기판에 다중 레이어 구조를 형성하는 과정을 나타내는 순서도이다.

- [0208] 먼저 제 2임시 기판을 준비한다(S2010). 이후 상기 기판 상에 릴리즈 레이저 반사층을 선택적으로 형성한다 (S2020). 상기 선택적 형성을 위해 포토공정 및 식각 공정이 수행될 수 있다. 또한 상기 반사층 형성을 위해 PVD(Physical Vapor Deposition) 또는 스퍼터링 공정이 수행될 수 있다.

- [0209] 상기 선택적 형성의 의미는 상기 제 2임시 기판 상에 반도체 발광 소자가 전사되지 않는 영역에 상기 릴리즈 레이저 반사 금속층을 형성하는 것이다. 편의상, 예를 들어, 제 2임시 기판으로 반도체 발광 소자가 전사되지 않는 영역을 제 1영역, 반도체 발광 소자가 전사되는 영역을 제 2영역이라고 정의한다.

- [0210] 이후, 릴리즈층을 형성한다(S2030). 상기 릴리즈층은 릴리즈 레이저 반사층을 포함한 제 2임시 기판의 전 영역에 형성한다.

- [0211] 상기 릴리즈층은 ITO, Amorphous Silicon, black carbon 또는 TiO2 나노 파티클을 포함한 레진 중 적어도 어느 하나를 포함할 수 있다.

- [0212] 마지막으로 상기 릴리즈층 상부에 보호층을 형성한다(S2040). 상기 보호층은 UV(Ultra Violet) 레진 또는 열경 화성 레진을 포함할 수 있다. 따라서, 전사 과정에서 사용되는 레이저에 의해 경화될 수 있으며, 이에 따라 상기 보호층의 하부에 형성되는 릴리즈층과 계면 박리를 가속화할 수 있다.

- [0213] 또한, 상기 보호층은 반도체 발광 소자가 배선 기판으로 전사되는 경우, 함께 전사되는 바, 상기 반도체 발광 소자의 굴절률을 고려하여 특정 굴절률로 형성할 수 있다. 즉, 상기 보호층의 제 1굴절률은 상기 반도체 발광 소자의 제 2굴절률보다 작게 형성할 수 있다. 예를 들어, 반도체 발광 소자가 GaN인 경우, 상기 반도체 발광 소자의 굴절률은 약 2.4인 바, 상기 보호층의 굴절률은 1.5 내지 2.3 사이의 값으로 설정하여 상기 반도체 발광 소자에서 방출된 빛이 다시 상기 소자 내부로 전반사되는 현상을 방지할 수 있다.

- [0214] 한편, 본 명세서의 전 취지에 비추어 보아, 당업자가 이해 가능한 수준에서, 도 20에 도시된 순서도의 일부 단계를 삭제, 변경하는 것도 본 발명의 다른 권리범위에 속한다.

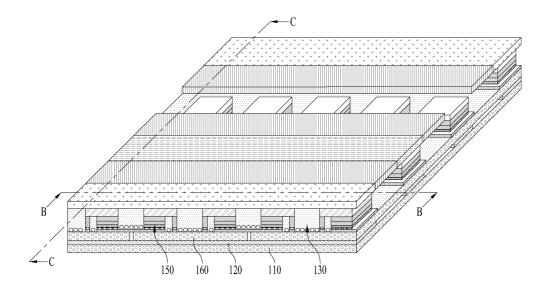

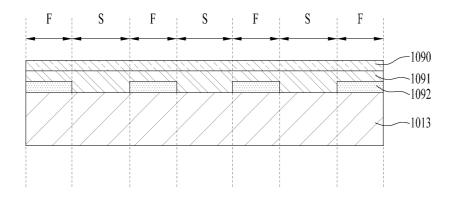

- [0215] 도 21은 도 20의 방법에 의해 형성된 제 2임시 기판의 다중 레이어 구조를 나타내는 단면도이다.

- [0216] 도 21에 도시된 바와 같이, 상기 제 2임시 기판(1013) 상부에 선택적으로 릴리즈 레이저 보호층(1092)이 위치한다. 또한, 상기 릴리즈 레이저 보호층을 포함한 제 2임시 기판(1013)의 전 영역에 릴리즈층(1091) 및 보호층(1090)이 위치한다.

- [0217] 상기 릴리즈 레이저 보호층(1092)이 위치한 영역은 도21에 도시된 바와 같이, F영역에 해당한다. 한편, 도 21의 S영역은 릴리즈 레이저 보호층이 형성되지 않는 영역으로, 전사 과정에서 반도체 발광 소자가 위치할 영역이다.

- [0218] 따라서, 제 2임시 기판(1013)의 후면부에 레이저를 조사하는 경우, 상기 레이저는 S영역의 릴리즈층(1091) 및 보호층(1090)에는 영향을 주게 되나, F영역은 릴리즈 레이저 반사층(1092)에 의해 상기 F영역의 릴리즈층(1091) 및 보호층(1090)에는 영향을 주기 어렵다.

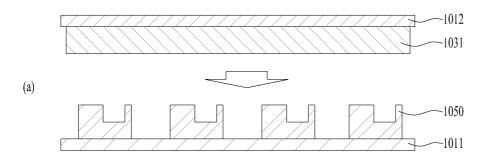

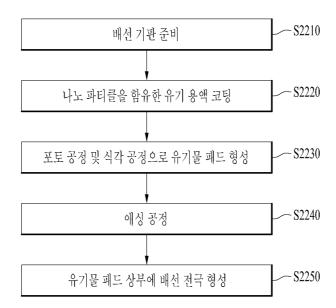

- [0219] 도 22는 불규칙한 요철 구조를 구비한 배선 전극을 제작하는 과정을 나타내는 순서도이다.

- [0220] 먼저, 배선 기판을 준비한다(S2210). 이후 상기 배선 기판 상에 나노 파티클을 함유한 유기 용액을 코팅한다 (S2220).

- [0221] 상기 유기 용액은 휘발 성분을 제거하여 유기층의 형태로 상기 배선 전극 상부에 존재한다. 이후, 상기 유기층에 대해 포토 공정 및 식각 공정을 수행하여, 반도체 발광 소자의 도전형 전극부와 대응하는 위치에 유기물 패드를 형성한다(S2230).

- [0222] 나아가 상기 유기물 패드의 표면 형상을 변화시키기 위해 애싱 공정을 수행한다(S2240). 마지막으로, 상기 유기물 패드의 상부에 배선 전극을 형성한다(S2250).

- [0223] 상기 애싱 공정을 통해 상기 유기물 패드의 표면은 불규칙한 요철 구조를 가지게 된다. 따라서 상기 유기물 패드 상부에 형성된 배선 전극 또한 불규칙한 요철 구조를 지니게 되는데, 보다 자세한 내용은 도 23에서 후술한다.

- [0224] 한편, 본 명세서의 전 취지에 비추어 보아, 당업자가 이해 가능한 수준에서, 도 22에 도시된 순서도의 일부 단계를 삭제, 변경하는 것도 본 발명의 다른 권리범위에 속한다.

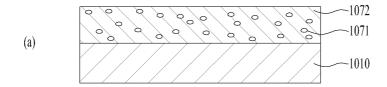

- [0225] 도 23은 불규칙한 요철 구조를 구비한 배선 전극을 제작하는 과정을 나타내는 단면도들이다.

- [0226] 도 23(a)는 배선 기판(1010) 상에 나노 파티클(1071)을 함유한 유기층(1072)을 형성한 이후의 단면도이다.

- [0227] 전술하였듯이, 나노 파티클(1071)을 함유한 유기 용액을 상기 배선 기판(1010) 에 코팅한다. 상기 코팅 방법으로는 스핀 코팅이 이용될 수 있다. 상기 스핀 코팅의 경우, 회전 속도와 시간의 조절을 통해 비교적 간단하게 코팅 두께를 조절할 수 있으며, 대면적의 유기 용액 코팅에 유리하다. 다만, 상기 코팅 방법은 예시적인 사항일뿐, 본 발명의 이에 한정되는 것은 아니다.

- [0228] 이후 소프트 베이킹(Baking) 공정을 통해 상기 유기 용액의 휘발성분(solvent)이 제거되고, 비교적 고체화된 유기층(1072)이 상기 배선 기판(1010)의 상부에 형성된다.

- [0229] 상기 유기층(1072)의 성분은 예를 들어, 감광성 유기 성분을 포함한다. 상기 감광성 유기 성분은 감광성 아크릴 레이트, PAC(Photo Active Compounds)일 수 있다.

- [0230] 또한, 상기 나노 파티클(1071)은 예를 들어, 10nm 내지 300nm의 무기물 또는 금속 성분일 수 있다.

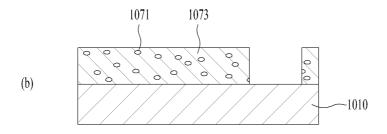

- [0231] 이후, 도 23(b)에 도시된 바와 같이, 상기 유기층(1072)에 대해 포토 공정 및 식각 공정을 수행하여, 반도체 발광 소자의 도전형 전극부와 대응하는 위치에 유기물 패드(1073)를 형성한다.

- [0232] 나아가, 상기 유기물 패드(1073)의 표면 형상을 변화시키기 위해, 상기 유기물 패드에 애싱 공정을 수행한다.

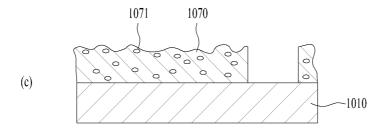

- [0233] 도 23(c)는 애싱 이후 상기 유기물 패드의 형상을 나타내는 단면도이다.

- [0234] 상기 애싱 공정을 통해, 예를 들어, 02 플라즈마에 상기 유기물 패드의 표면을 수 초간 노출시킴으로써 상기 유기물 패드의 표면의 형상을 변형시키게 된다. 02 플라즈마는 나노 파티클보다는 유기물을 제거하는데 효과적인 바, 플라즈마 처리가 지속될수록 유기물 패드 내의 나노 파티클(1071)은 유기물 패드(1070)의 표면으로 드러나

게 된다. 따라서 애싱 공정 이후, 상기 유기물 패드(1070)의 표면은 불규칙한 요철 구조를 형성한다.

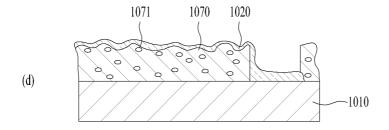

- [0235] 이후, 도 23(d)에 도시된 바와 같이, 상기 배선 전극(1020)은 상기 불규칙한 요철 구조를 구비한 유기물 패드 (1070)의 상부에 형성된다. 따라서, 상기 배선 전극(1020) 또한 상기 유기물 패드(1070)의 표면에 돌출된 나노 파티클(1071)에 의해 표면 형상이 불규칙한 요철 구조를 구비하게 된다.

- [0236] 상기 배선 기판(1010) 상에 위치한 배선 전극(1020)에 있어서, 상기 불규칙한 요철 구조 및 상기 유기물 패드가 효과적인 이유는 다음과 같다.

- [0237] 전술하였지만, 배선 전극은 반도체 발광 소자의 도전형 전극부와 전기적으로 연결되는 영역이다. 또한 본 발명에서는, 상기 전극부와 상기 배선 전극 사이에는 이방 전도성 접착 페이스트층이 존재하고, 상기 페이스트층의 도전성 입자에 의해 전기적으로 연결된다. 따라서 상기 도전성 입자가 상기 도전형 전극부 또는 상기 배선 전극과 정확히 접촉하지 않으면 불량이 발생하게 된다. 또한 상기 도전성 입자가 정확히 접촉되더라도, 접착 과정에서 강한 충격에 의해 상기 배선 전극 또는 상기 도전형 전극부가 손상을 입을 수 있다.

- [0238] 따라서, 불규칙한 요철 구조의 경우, 상기 도전성 입자와 접촉 면적을 늘림으로써, 도전성 입자와 배선 전극간 의 접착력 및 접착 확률을 증가시켜 상기 불량을 예방할 수 있다. 또한 배선 전극 하부에 형성된 상기 유기물 패드는 상기 도전성 입자와 상기 배선 전극의 접착 과정에서 발생하는 충격을 완화시켜주어 상기 배선 전극의 손상을 방지한다.

- [0239] 정리하면, 본 발명은 이방 전도성 접착 페이스트층을 이용하여 반도체 발광 소자를 배선 기판에 전사함과 동시에 배선 공정을 수행하게 한다. 상기 이방 전도성 접착 페이스트층은 상기 반도체 발광 소자가 배선 전극과 연결되는 영역 및 그 주변부만 형성되어 소자 간의 쇼트 불량의 위험성을 감소시킨다. 또한 상기 배선 전극은 불규칙한 요철 구조 및 하부에 유기물 패드를 구비하여, 상기 페이스트층의 도전성 입자와 접촉하기 용이하게 하고, 접촉 시 충격을 완화시킨다. 따라서 본 발명을 이용하면, 반도체 발광 소자가 안정적으로 배선 기판에 전사됨과 동시에 쇼트(short) 및 오픈(open) 불량을 최소화하는 배선 공정이 수행되는 효과를 가질 수 있다.

- [0240] 이상의 설명은 본 발명의 기술 사상을 예시적으로 설명한 것에 불과한 것으로서, 본 발명이 속하는 기술 분야에 서 통상의 지식을 가진 자라면 본 발명의 본질적인 특성에서 벗어나지 않는 범위에서 다양한 수정 및 변형이 가능할 것이다.

- [0241] 따라서, 본 발명에 개시된 실시 예들은 본 발명의 기술 사상을 한정하기 위한 것이 아니라 설명하기 위한 것이고, 이러한 실시 예에 의하여 본 발명의 기술 사상의 범위가 한정되는 것은 아니다.

- [0242] 본 발명의 보호 범위는 아래의 청구범위에 의하여 해석되어야 하며, 그와 동등한 범위 내에 있는 모든 기술 사 상은 본 발명의 권리범위에 포함되는 것으로 해석되어야 할 것이다.

# 부호의 설명

[0243] 1010 : 배선 기판 1020 : 제 1전극

1030 : 절연층 1040 : 제 2전극

1050 : 반도체 발광 소자 1052 : 제 2도전형 전극

1053 : 제 2도전형 반도체층 1054 : 활성층

1055 : 제 1도전형 반도체층 1056 : 제 1도전형 전극

1070 : 유기물 패드 1080 : 이방 전도성 접착 페이스트층

1081 : 도전성 입자 1090 : 보호층

# 도면1

# 도면3a

# 도면3b

# 도면5a

# *도면5b*

# 도면5c

도면7

| 专利名称(译)     | 使用微型LED的显示装置及其制造方法                                      |         |            |

|-------------|---------------------------------------------------------|---------|------------|

| 公开(公告)号     | KR1020190092331A                                        | 公开(公告)日 | 2019-08-07 |

| 申请号         | KR1020190087673                                         | 申请日     | 2019-07-19 |

| 申请(专利权)人(译) | LG电子公司                                                  |         |            |

| [标]发明人      | 최환준<br>위경태                                              |         |            |

| 发明人         | 최환준<br>위경태                                              |         |            |

| IPC分类号      | H01L27/15 H01L33/00 H01L33/36 H01L33/50                 |         |            |

| CPC分类号      | H01L27/156 H01L33/005 H01L33/36 H01L33/50 H01L2224/1144 |         |            |

| 代理人(译)      | Gimyongin<br>铁干扰                                        |         |            |

| 外部链接        | Espacenet                                               |         |            |

|             |                                                         |         |            |

## 摘要(译)

在本说明书中,公开了一种微型LED显示装置及其制造方法,其中,各向异性导电粘合剂膏层仅预先形成在半导体发光装置的导电电极部分和与其周围的部分上,以及然后,将半导体发光器件转移到布线基板上,从而通过该转移执行稳定的布线工艺。根据本发明的实施例,一种使用多个半导体发光器件的显示装置包括:基板;有机垫位于基板上,具有不规则的凹凸结构;位于有机焊盘上的布线电极;各向异性导电胶糊层,其包括位于布线电极上的导电颗粒;半导体发光器件,其位于各向异性导电粘合剂糊剂层上,并通过糊剂层的导电粒子与布线电极电连接;保护层设置在未连接至布线电极的半导体发光器件的上侧表面上。有机垫包括多个纳米颗粒,并且具有其中多个纳米颗粒中的至少一个纳米颗粒暴露于有机垫的表面的结构。